ZHCU923A October 2020 – February 2022

- 商标

- 1引言

- 2J7200 EVM 概述

- 3EVM 用户设置/配置

- 4J7200 EVM 硬件架构

- 5功能安全

- 6修订历史记录

4.15 FPD 接口(音频解串器)

注: J7200 EVM 不支持 CP 板上的 FPD(音频)接口。

CP 板支持 TI 的 FPD-Link III 解串器 IC(制造商器件型号为 DS90UB926QSQE),以使用 HSD 连接器(制造商器件型号为 D4S20G-400A5-C)恢复来自调谐器接口的音频信号。解串器将通过数字链路恢复多达八个数字音频通道和 I2C 通道。

该音频信号通过 1:3 多路信号分离器 (SN74CBT16214CDGGR) 连接到 J7200 SoC 的 McASP1 端口。GPIO 扩展器和 EVM 配置 DIP 开关 (SW3) 均支持通道选择。

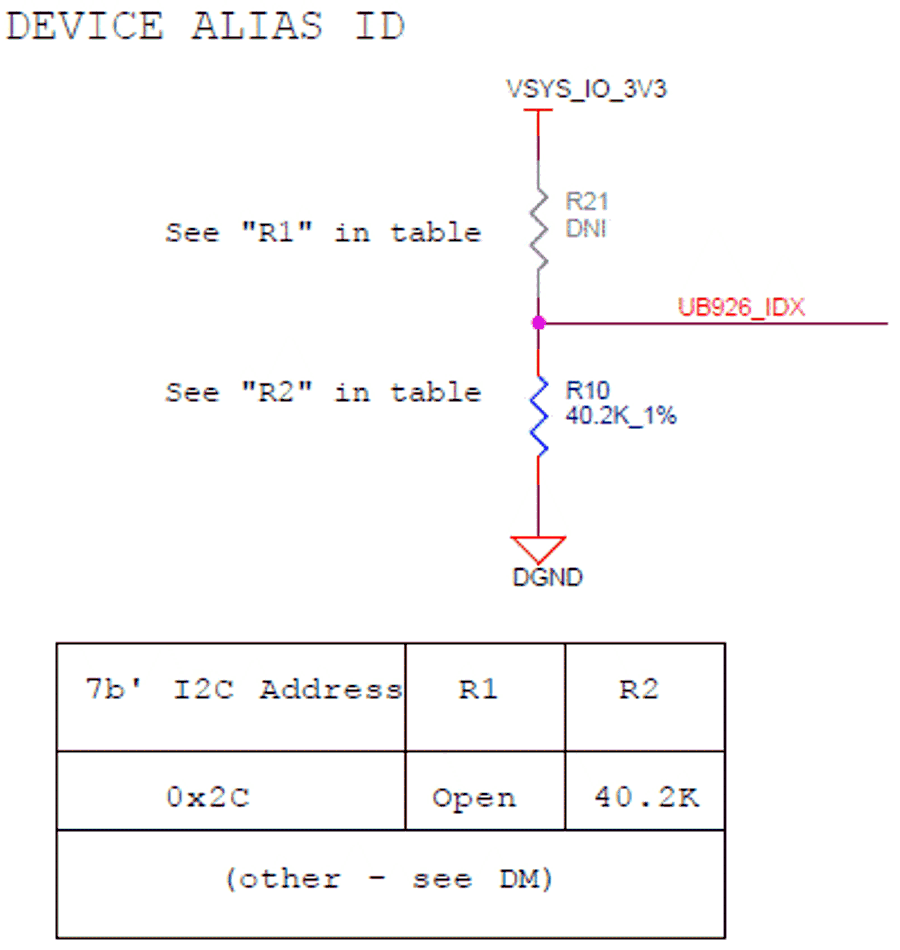

J7200 的 I2C1 信号用于解串器控制。ID[X] 引脚上提供了一个 40.2KΩ 下拉电阻器,以将 7'b I2C 地址设置为 0x2C。

图 4-33 FPD-Link UB926 ID 设置电路

图 4-33 FPD-Link UB926 ID 设置电路使用电源开关 TPS1H100AQPWPRQ1 为 HSD 连接器提供 +12V 电源,从而为 FPD Link-III 调谐器扩展板供电。电源开关通过 GPIO 扩展器信号 (UB926_PWR_SW_CNTRL) 进行控制。

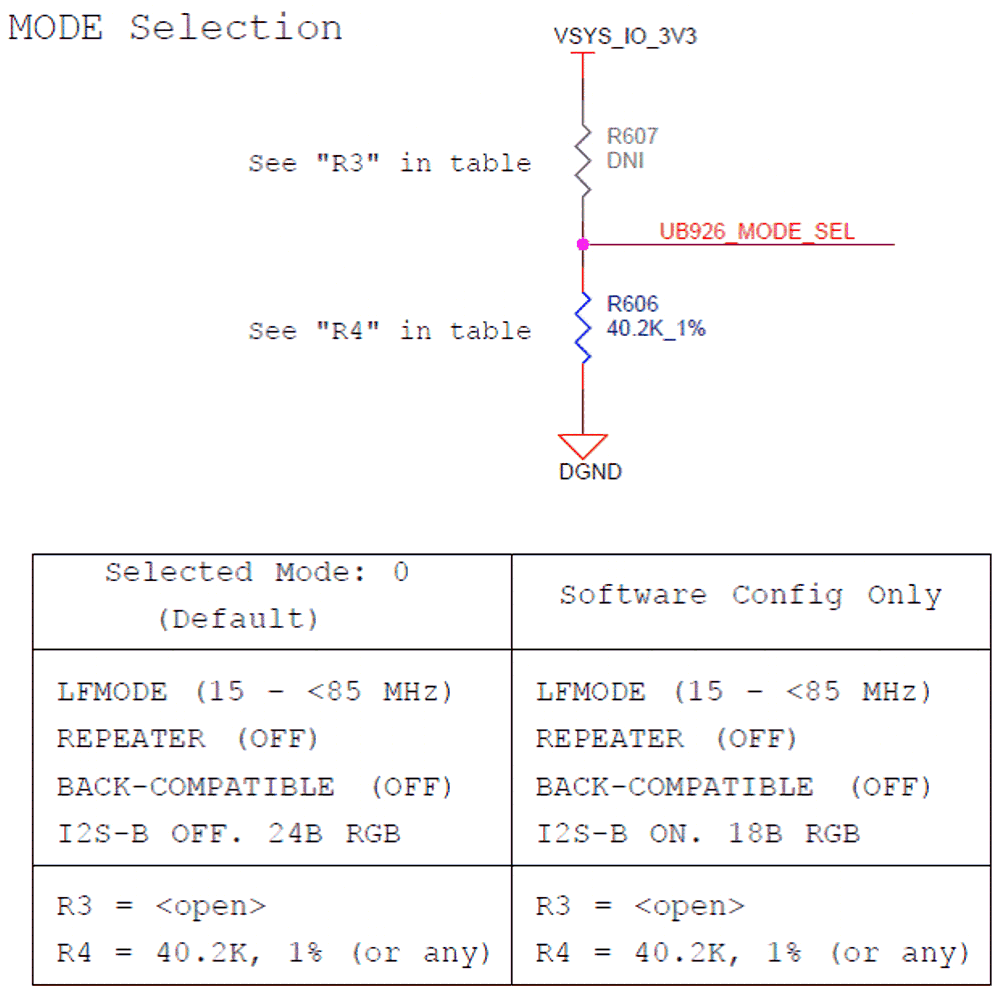

图 4-34 显示了解串器的模式选择。

图 4-34 FPD-Link UB926 模式选择电路

图 4-34 FPD-Link UB926 模式选择电路表 4-21 显示了 HSD 连接器 J1 的引脚排列。

表 4-21 FPD 音频解串器 HSD 连接器引脚排列

| 引脚编号 | 信号 |

|---|---|

| 1 | GND |

| 2 | RIN_N |

| 3 | 电源 (12V) |

| 4 | RIN_P |