ZHCU923A October 2020 – February 2022

- 商标

- 1引言

- 2J7200 EVM 概述

- 3EVM 用户设置/配置

- 4J7200 EVM 硬件架构

- 5功能安全

- 6修订历史记录

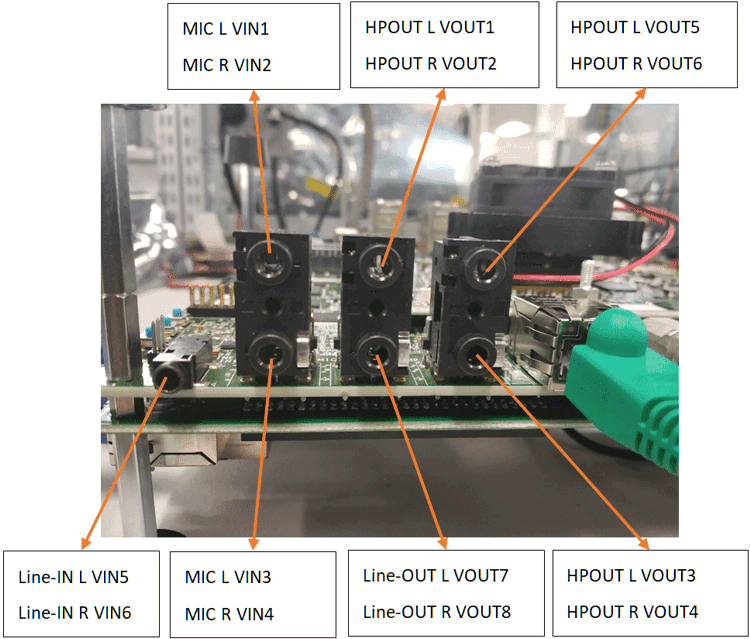

4.13.5 端口映射

通用处理器板音频端口按照如下方式进行映射。

- 提供了 3 个标准 3.5mm 堆叠式立体声音频插孔(制造商器件型号为 STX-4235-3/3-N):

- 2x – 麦克风输入,1x – 线路输出和 3x – 耳机输出。

- 提供了 1 个标准 3.5mm 立体声音频插孔(制造商器件型号为 SJ-3524-SMT-TR):

- 1x – 线路输入接口。

图 4-29 音频端口接口分配

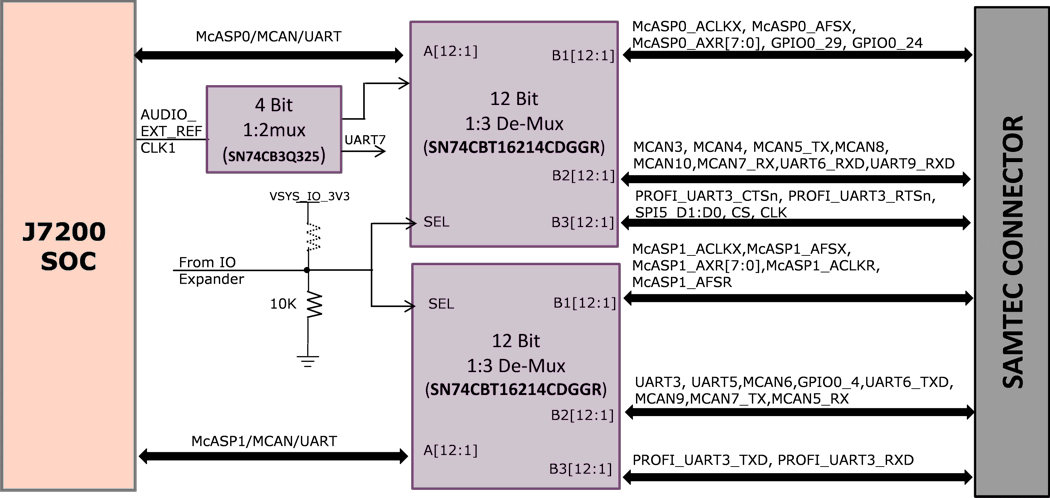

图 4-29 音频端口接口分配J7200 SoC 的 McASP0 和 McASP1 与 UART 和 MCAN 接口进行多路复用。J7200 SOM 包括两个 1:3 多路信号分离器(制造商器件型号 SN74CBTLV16292GR),以支持 CP 板上的音频编解码器和跟踪功能以及 J7x GESI 扩展板上的 MCAN/LIN。McASP/TRACE 接口的默认通道选择通过电阻器自举来实现,而 J7200 SoC 上 GPIO 扩展器的 GPIO 将会更改该配置。

J7200 SoC 的 AUDIO_EXT_REF_CLK1 用于音频编解码器的系统参考时钟输入。4 位 1:2 多路复用器 IC 用于将时钟输入路由到 McASP/MCAN 多路复用器,如图 4-30 所示。

图 4-30 McASP/TRACE/MCAN 多路复用器电路

图 4-30 McASP/TRACE/MCAN 多路复用器电路表 4-20 用于 MCASP/TRACE/MCAN 选择的 1:3 多路复用器真值表

| MUX_SEL2 | MUX_SEL1 | MUX_SEL0 | 功能 |

|---|---|---|---|

| 高电平 | 高电平 | 低电平 | 端口 0 = B1 端口 |

| 高电平 | 高电平 | 高电平 | 端口 0 = B2 端口(默认) |

| 高电平 | 低电平 | 高电平 | 端口 0 = B3 端口 |

端口 B1:McASP0/1 和 TRACE

端口 B2:MCAN/UART

端口 B3:PROFI_UART/SPI