ZHCACT1D September 2022 – May 2025 AM2612 , AM2612-Q1 , AM2631 , AM2631-Q1 , AM2632 , AM2632-Q1 , AM2634 , AM2634-Q1 , AM263P2 , AM263P2-Q1 , AM263P4 , AM263P4-Q1

14.3.2 3.3V I/O 电源主要布局注意事项 - ZFG

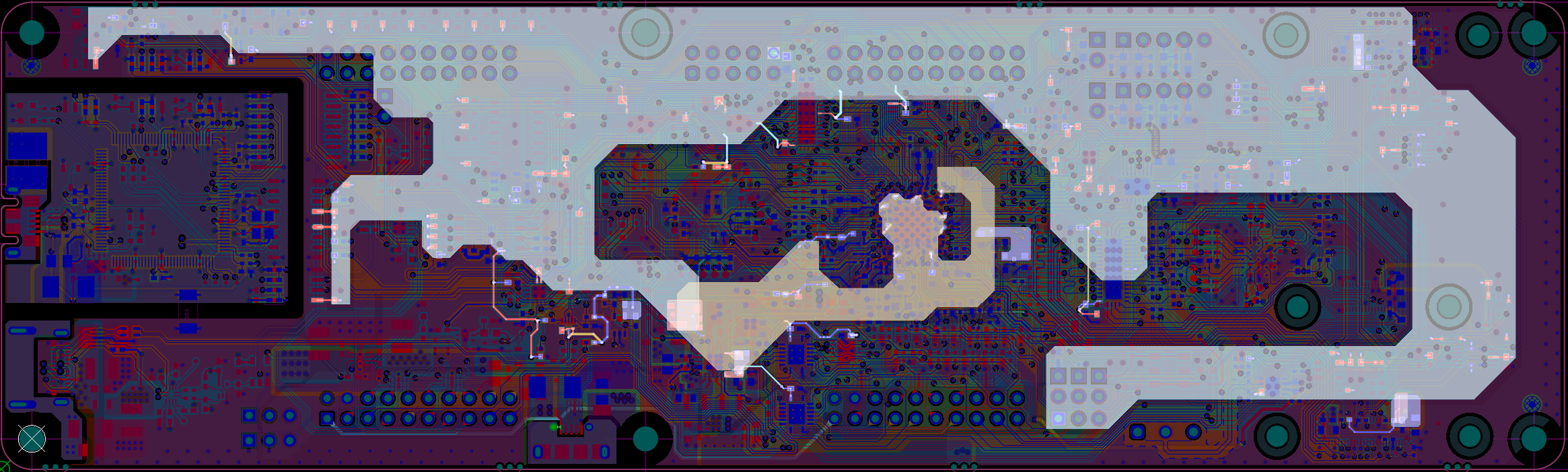

使用 AM261x LaunchPad EVM (LP-AM261) 探索 AM261x ZFG 器件上的 3.3V 电源系统,从 PMIC (TPS650366) 的 3.3V 降压输出,经由电路板电源平面,并终止于 BGA 大容量和每引脚去耦电容器阵列。PMIC 3.3V 降压输出为所有 AM261x 数字 I/O、模拟 I/O 和其余 LaunchPad 负载供电。这在所有 3.3V 数字电平 I/O 共用一个公共电源的大多数设计中很常见。本地 AM261x 3.3V 模拟电源网的额外滤波是通过铁氧体磁珠 FB2 和相关电容器的 LC 滤波器完成的。这用于创建一个低 IR 压降低通滤波器,该滤波器将衰减 PMIC 降压输出的高频开关谐波。

- 需要对所有电源和接地回路过孔扇出使用宽 10mil 的走线。

- 3.3V I/O 电源往往在系统中的多个器件之间共享,建议在 PCB 上使用非常宽的电源平面进行布线,以最大限度地减少所有元件(包括 AM261x SoC)的 IR 压降。

- 需要使用紧密耦合的相邻接地回路参考平面,以实现更佳的瞬态性能和 EMI 耦合。

- 需要使用覆盖 BGA 3.3V 电源引脚区域的宽电源平面入口,以实现更小的 IR 压降和更佳的瞬态性能。

- 采用较大封装、较低频率的大容量电容需放置在 MCU BGA 附近,过孔需直接连接到电源平面路径。

- 采用较小封装、较高频率的去耦电容需要直接放置在 BGA 扇出过孔上,并以尽可能小的狗骨配置连接到电源和接地回路过孔。

图 14-17 AM261x LaunchPad 摘录 – 第 3 层和第 4 层上的 3.3V 数字和模拟电源平面

图 14-17 AM261x LaunchPad 摘录 – 第 3 层和第 4 层上的 3.3V 数字和模拟电源平面 图 14-18 AM261x LaunchPad 摘录 – 3.3V 数字 I/O BGA 引脚排列和 PMIC 输出

图 14-18 AM261x LaunchPad 摘录 – 3.3V 数字 I/O BGA 引脚排列和 PMIC 输出 图 14-19 AM261x LaunchPad 摘录 - 3.3V 模拟 IO BGA 引脚排列

图 14-19 AM261x LaunchPad 摘录 - 3.3V 模拟 IO BGA 引脚排列 图 14-20 AM261x LaunchPad 摘录 – 第 3 层上的 3.3V 数字电源

图 14-20 AM261x LaunchPad 摘录 – 第 3 层上的 3.3V 数字电源 图 14-21 AM261x LaunchPad 摘录 – 3.3V 数字电源去耦安装,第 6 层

图 14-21 AM261x LaunchPad 摘录 – 3.3V 数字电源去耦安装,第 6 层用于 4 层 PCB 的 1.2V 内核数字电源走线方案正在研究中,本文档的日后修订版中可能会包含相关内容。