ZHCACT1D September 2022 – May 2025 AM2612 , AM2612-Q1 , AM2631 , AM2631-Q1 , AM2632 , AM2632-Q1 , AM2634 , AM2634-Q1 , AM263P2 , AM263P2-Q1 , AM263P4 , AM263P4-Q1

12 层堆叠

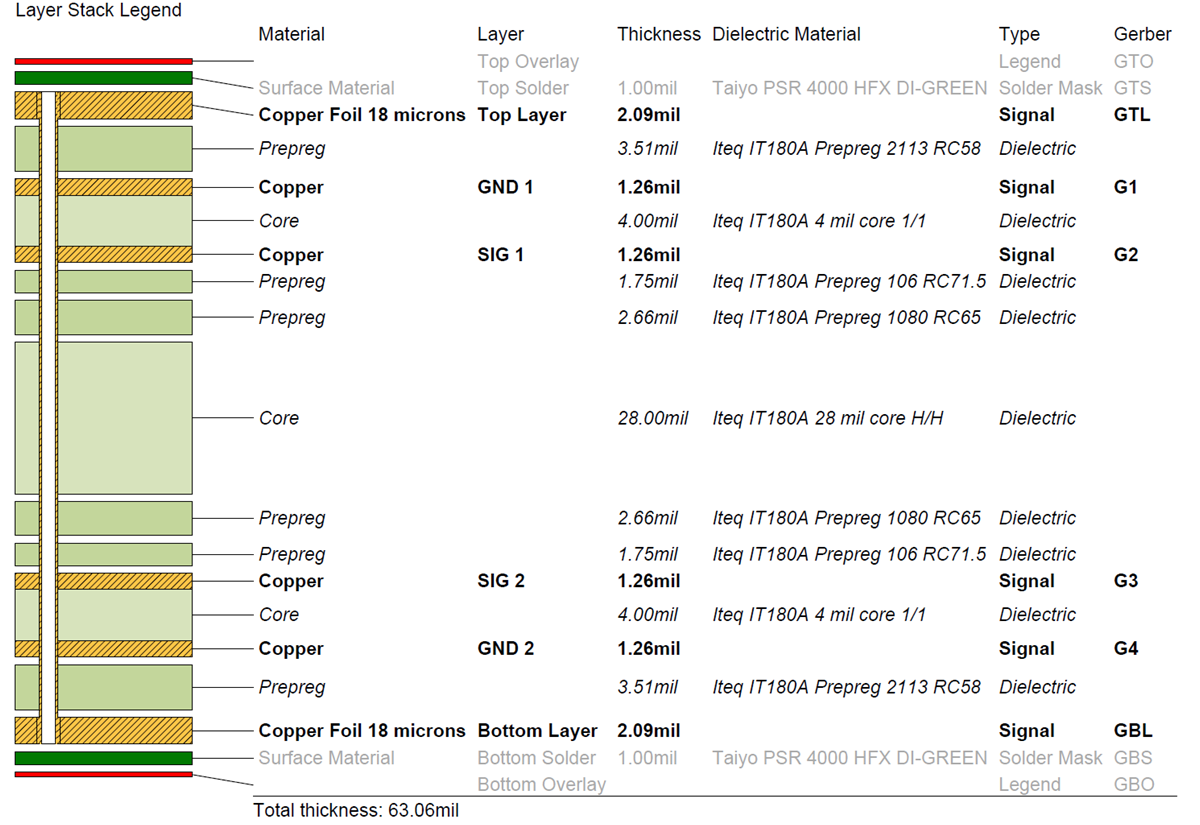

AM263x、AM263Px 以及 AM261x MCU 的四个封装之一采用 ZCZ0324A 324 焊球、0.8 毫米间距、18 x 18 全 NFBGA 阵列 15mm x 15mm 封装(在本文档中称为“ZCZ 封装”)。该封装上的间距较大可实现低层数功耗和完整信号扇出。对于 LP-AM263 EVM,6 层堆叠设计能够在器件上完整排布所有电源和信号引脚,以实现电路板的 LaunchPad 外形。下面的 LP-AM263 LaunchPad 堆叠代表了目前 ZCZ 封装设备最优化的堆叠示例。

对于 ZCZ 封装,很可能实现更低层数的堆叠,尤其是在考虑部分信号扇出设计时。不过,TI 尚未探索这些问题。

图 12-1 LP-AM263 堆叠

图 12-1 LP-AM263 堆叠下表介绍了 AM261x MCU 的其他三个封装:

表 12-1 AM261x 封装尺寸

| 封装名称(类型、焊球数) | 封装尺寸 | BGA 间距 | BGA 阵列 |

|---|---|---|---|

| ZNC (NFBGA,293) |

10mm x 10mm | 0.5mm | 19 x 19 |

| ZEJ (NFBGA,256) |

13mm x 13mm | 0.8mm | 16 x 16 |

| ZFG (NFBGA,304) |

13.25mm x 13.25mm | 0.65mm | 20 x 20 |

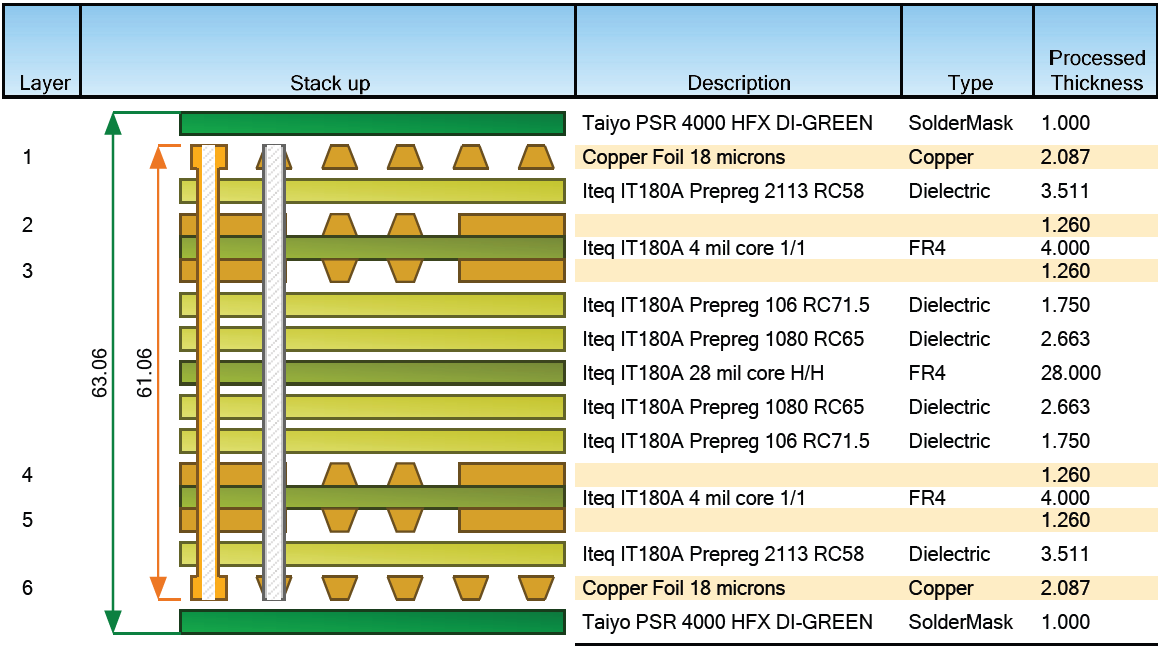

对于 LP-AM261 EVM,6 层堆叠设计能够在 ZFG 封装器件上完整排布所有电源和信号引脚,以实现电路板的 LaunchPad 外形。下面的 LP-AM261 LaunchPad 堆叠代表了目前针对 ZFG 封装优化的全系统堆叠示例:

图 12-2 LP-AM261 堆叠

图 12-2 LP-AM261 堆叠TI 一直在探索 AM261x ZFG 和 ZNC 封装的较低层数堆叠。下图是采用 AM261x ZFG 或 ZNC 封装尺寸的 PCB 系统 4 层堆叠的示例:

图 12-3 AM261x ZFG/ZNC PCB 系统堆叠

图 12-3 AM261x ZFG/ZNC PCB 系统堆叠