ZHCACT1D September 2022 – May 2025 AM2612 , AM2612-Q1 , AM2631 , AM2631-Q1 , AM2632 , AM2632-Q1 , AM2634 , AM2634-Q1 , AM263P2 , AM263P2-Q1 , AM263P4 , AM263P4-Q1

6.1.3 AM261x OSPI 和 QSPI 引导引脚要求

以下引脚在器件的引导 ROM 中配置,用于实现从 OSPI(或 QSPI)闪存器件引导。必须使用这些引脚来连接 AM261x MCU 和闪存器件。

| 封装名称 | 函数名称 | GPIO 编号 | PinMux 模式 # |

|---|---|---|---|

| OSPI0_CSn0 | OSPI0_CSn0 | 0 | 0 |

| OSPI0_CLK0 | OSPI0_CLK0 | 2 | 0 |

| OSPI0_D0 | OSPI0_D0 | 3 | 0 |

| OSPI0_D1 | OSPI0_D1 | 4 | 0 |

| OSPI0_D2 | OSPI0_D2 | 5 | 0 |

| OSPI0_D3 | OSPI0_D3 | 6 | 0 |

| MCAN0_RX | OSPI0_D4 | 7 | 2 |

| MCAN0_TX | OSPI0_D5 | 8 | 2 |

| MCAN1_RX | OSPI0_D6 | 9 | 2 |

| MCAN1_TX | OSPI0_D7 | 10 | 2 |

| 封装名称 | 函数名称 | GPIO 编号 | PinMux 模式 # |

|---|---|---|---|

| EPWM9_B | OSPI0_CSn0 | 62 | 6 |

| MCAN1_TX | OSPI0_CLK0 | 10 | 5 |

| OSPI0_CLK | OSPI0_D0 | 2 | 4 |

| PR1_PRU0_GPIO9 | OSPI0_D1 | 70 | 6 |

| MCAN0_RX | OSPI0_D2 | 7 | 5 |

| PR1_PRU0_GPIO2 | OSPI0_D3 | 69 | 2 |

| UART1_TXD | OSPI0_D4 | 76 | 2 |

| PR1_PRU0_GPIO0 | OSPI0_D5 | 67 | 2 |

| MCAN0_TX | OSPI0_D6 | 8 | 2 |

| PR1_PRU0_GPIO1 | OSPI0_D7 | 68 | 2 |

OSPI 复位的实现 1:PORz、WARMRESETn

从 OSPI 闪存引导时,必须在向 AM261x 器件加载数据之前对闪存进行复位。将 AM261x MCU 的 PORz 或 WARMRESETn 直接连接到闪存器件,可确保在系统上电时将闪存复位,因为在引导期间,PORz 和 WARMRESETn 处于低电平,在电源稳定后会变为高电平。请确保 PORz 或 WARMRESETn 与闪存器件使用正确的 IO 电压电平。

图 6-7 使用 PORz 或 WARMRESETn 复位 OSPI 闪存

图 6-7 使用 PORz 或 WARMRESETn 复位 OSPI 闪存OSPI 复位的实现 2:其他采用 OSPI0_RESET_OUT0 PinMux 的 GPIO(建议)

建议采用此实现方案,因为同时提供硬件和软件复位选项,并且不需要额外的缓冲区。根据器件数据表中的引脚多路复用配置,引导完成后,表 6-9 中列出的任意一个 AM261x GPIO 引脚均可用作 OSPI 闪存复位逻辑的复位输入。请确保复位逻辑输入和输出的电压电平与闪存器件的 IO 电压一致。建议采用的实施方案如 图 6-8 所示。

图 6-8 使用 OSPI0_RESET_OUT0 和 PORz、WARMRESETn 复位 OSPI 闪存

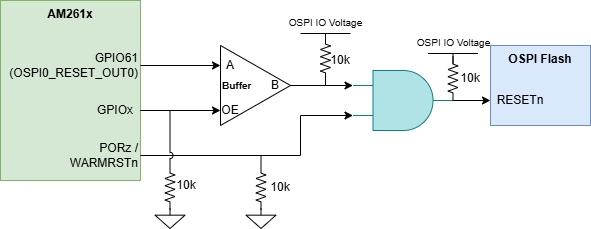

图 6-8 使用 OSPI0_RESET_OUT0 和 PORz、WARMRESETn 复位 OSPI 闪存OSPI 复位的实现 3:缓冲后的 GPIO61

GPIO61 仍可通过软件作为 OSPI0_RESET_OUT0,用于复位 OSPI 闪存。必须将该信号连接到与门,并将 PORz 和 WARMRESETn 作为另一输入,以驱动闪存器件的复位输入。不过,在启动时必须对 GPIO61 信号进行缓冲处理,以防止低电平信号传播到 OSPI 复位逻辑。这可以通过使用下拉电阻器配置缓冲器输出使能引脚并使用 AM261x 器件中的任何 GPIO 驱动输出使能来实现。请确保复位逻辑输入和输出的电压电平与闪存器件的 IO 电压一致。

图 6-9 使用缓冲后的 GPIO61 和 PORz、WARMRESETn 来复位 OSPI 闪存

图 6-9 使用缓冲后的 GPIO61 和 PORz、WARMRESETn 来复位 OSPI 闪存