ZHCABZ5A November 2021 – December 2022 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1

3.2.4 通信外设

F2800x 器件包含不同数量的以下通信外设:

- 控制器局域网 (CAN/DCAN)

- 模块化控制器局域网 (MCAN/CAN FD)

- 内部集成电路 (I2C)

- 电源管理总线 (PMBus) 接口

- 串行通信接口 (SCI)

- 串行外设接口 (SPI)

- 本地互连网络 (LIN)

- 快速串行接口 (FSI)

- 主机接口控制器 (HIC)

鉴于这些外设的性质及其不同的通信方式,每个系统在设计时都必须考虑到预定的通信外设支持。板级接口(包括 I2C、PMBus 和 SPI)连接到板上其他器件或通过电路板连接到其他器件。由于这些驱动器通常直接运行,因此务必密切注意驱动能力和布线长度。这些因素取决于这些信号的选定频率。

使用 CAN 时,建议在电路板上实施外部振荡器,而不是使用内部振荡器。根据所需的 CAN 参数(如位时间设置、比特率、总线长度和传播延迟),片上零引脚振荡器的精度可能不符合 CAN 协议的要求。有关这方面的更多信息,请参阅Topic Link Label3.6.1以及 DCAN 模块的编程示例和调试策略。

特别是对于 I2C,建议使用外部上拉电阻器将 SDAA 和 SCLA 引脚拉高。太强的上拉(较小的电阻器阻值)会阻止 I2C 引脚被有效地驱动为低电平,而太弱的上拉(较大的电阻器阻值)会影响通信速度。应根据功耗和速度之间的折衷来选择阻值。要计算上拉电阻器的理想范围,请参阅应用报告 I2C 总线上拉电阻器计算。

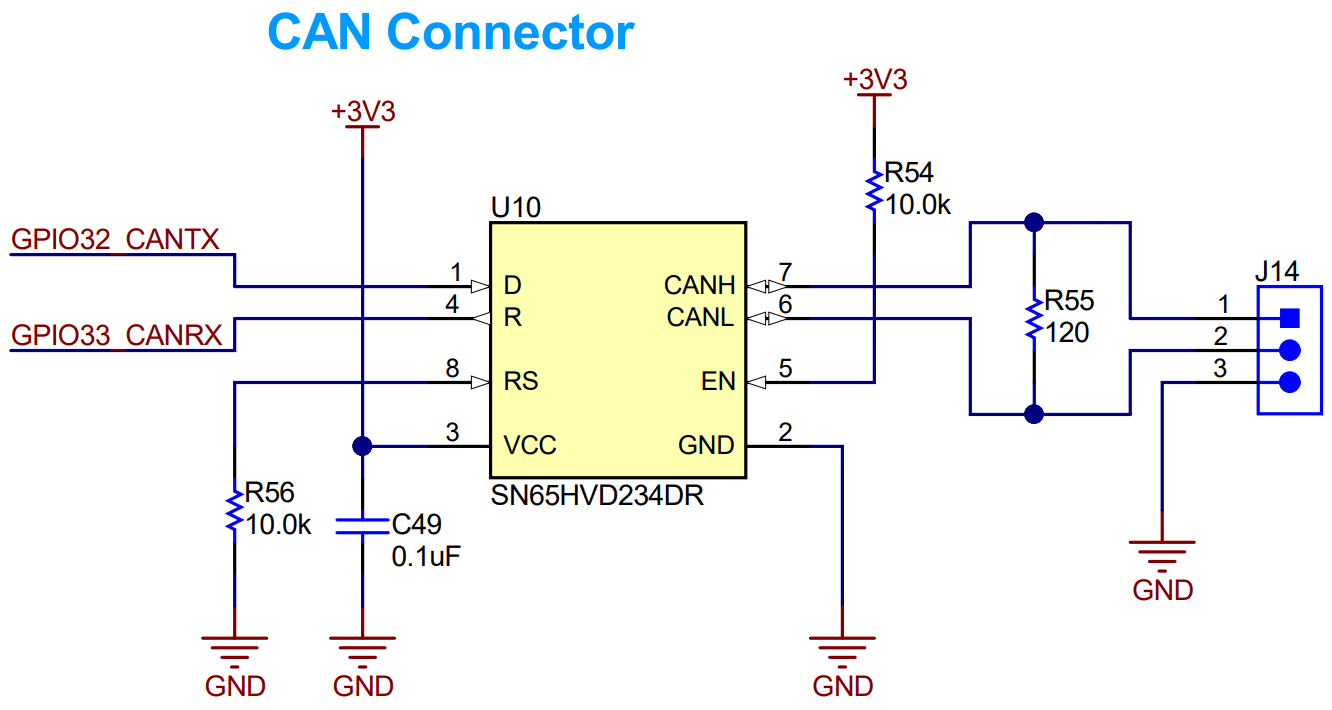

SCI、CAN、LIN 和 FSI 接口可连接两个或更多在不同处理器下运行的电路板。这些端口通常需要专用的收发器器件来转换电信号,从而降低噪声并与其他器件上的端口实现通信。使用通信收发器时,某些收发器可能需要在 MCU 的通信引脚上使用上拉电阻器。可根据收发器的数据表验证该要求。

图 3-5 LAUNCHXL-F280049C 中的 CAN 收发器

图 3-5 LAUNCHXL-F280049C 中的 CAN 收发器 图 3-6 典型的 RS-232 收发器

图 3-6 典型的 RS-232 收发器SCI 通信外设是一个 2 线异步串行端口,具有两个外部引脚 SCITXD(SCI 发送 - 输出)和 SCIRXD(SCI 接收 - 输入)。该协议通常称为 UART,C2000 器件上的该协议使用标准 NRZ 格式。对于某些收发器实现,建议在 SCI-RX 引脚上连接一个上拉电阻器,从而允许信号在不被驱动的情况下返回到高逻辑电平。这可以防止 GPIO 引脚在可能导致错误和增加电流消耗的电平值之间浮动。可使用所用的特定收发器的数据表验证该上拉电阻器要求。当使用某些类型的收发器来确保 SCI 模块的确定性操作时,尤其有必要连接上拉电阻器。应在系统内选择性使用和测试该电阻器阻值,因为理想值在很大程度上取决于特定应用。太弱的上拉(较大的电阻值)会阻止电阻器在实际电路中通过另一个器件上拉三态或浮动输出。同样,太强的上拉(较小的电阻值)会阻止输出信号通过另一个器件切换。可以先从 10kΩ 测试阻值。有关 SCI 传输调试和故障排除的更多信息,请参阅 E2E 上的 SCI 常见问题解答主题。

有关各种通信外设协议的其他参考资料,请参阅以下文档: