ZHCABZ5A November 2021 – December 2022 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1

4.1.3 层堆叠

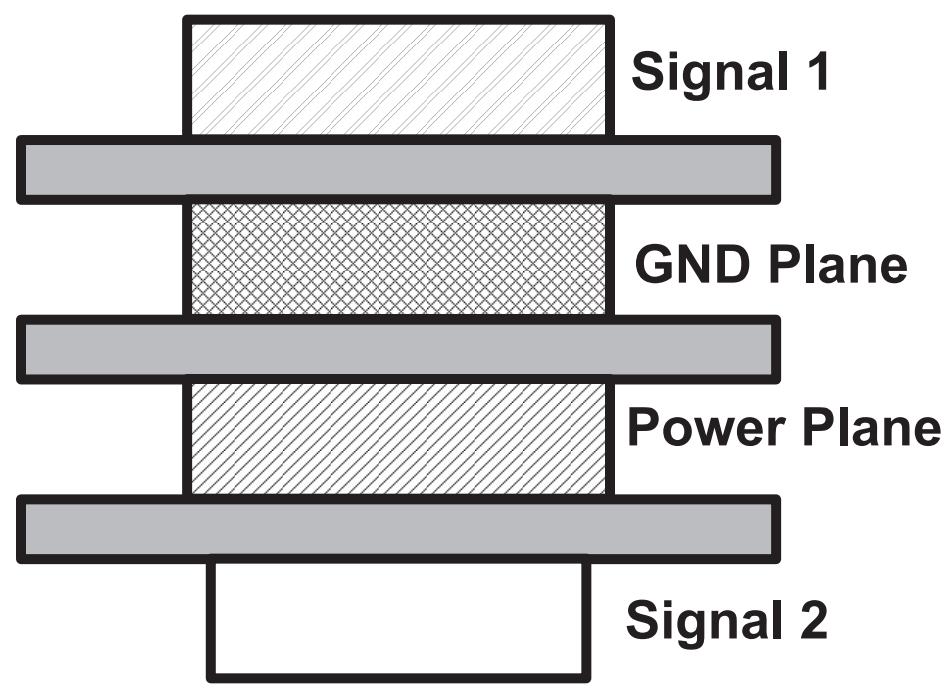

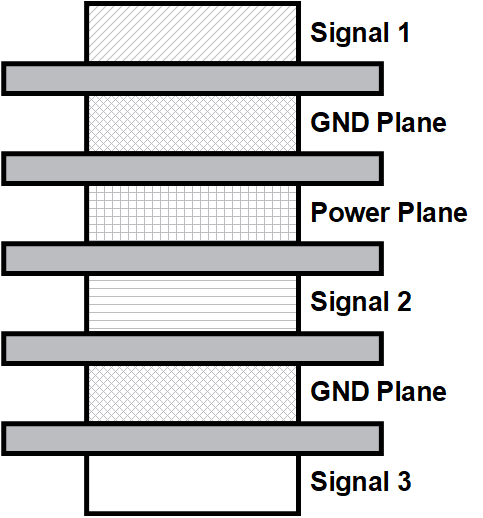

电路板层数和层堆叠的选择取决于 PCB 上所需的连接数量以及 PCB 的生产成本。4 层或更多层电路板通常是 C2000 器件的最佳选择。这使设计人员能够实现干净的接地平面和分割的电源平面。在配置方面,使用了两个图来展示常见的 4 层和 6 层电路板堆叠。4 层电路板堆叠包括信号/元件层、接地平面、分割的电源平面(3.3V、1.2V 等)和信号/元件层。对于 6 层电路板,堆叠如下:信号/元件层、接地平面、分割的电源平面(3.3V、1.2V 等)、信号层、另一个接地平面和信号/元件层。

图 4-1 4 层电路板的层堆叠

图 4-1 4 层电路板的层堆叠 图 4-2 6 层电路板的层堆叠

图 4-2 6 层电路板的层堆叠