ZHCABZ5A November 2021 – December 2022 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1

3.4.1 电源要求

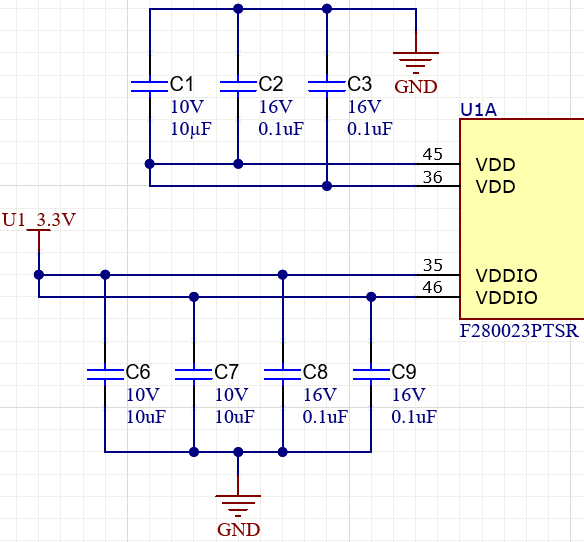

确保器件电源稳定且抗噪声的一个重要方面是每个电源引脚都具有接地的去耦/旁路电容器。这些有助于限制噪声传播到系统的其他区域,尤其是低电平模拟信号。去耦电容器充当滤波器和临时储能器,可充分减少电源上的压降/尖峰,从而为器件提供更稳定的电源解决方案。

图 3-9 VDD 引脚上的去耦电容器

图 3-9 VDD 引脚上的去耦电容器当使用外部稳压器(在受支持的器件上)为 VDD 供电时,所有 VDD 引脚应连接到相同的 1.2V 电源轨。这些引脚需要连接去耦电容器以确保实现稳定的电压电源。该去耦电容器的容值取决于器件,因此请参阅器件特定数据表以了解所需的 CVDD 值。同样,VDDA 和 VDDIO 电源引脚也需要连接去耦电容器来维持稳定的电压电源。在所有器件上,所有模拟电源引脚 (VDDA) 都应包含一个连接到模拟地 (VSSA) 的最小 2.2µF 的去耦电容器。数字 I/O 电源 (VDDIO) 需要在每个电源引脚附近有一个最小 0.1µF 的去耦电容器,如上图所示。对于某些器件,还建议放置一个额外的大容量电容器 CVDDIO,在所有引脚之间共享。该大容量电容值取决于所使用的稳压器,因此请参阅器件特定数据表。

需要特别注意的是 F28004x 器件,该器件包含一个内部直流/直流稳压器电源引脚 (VDDIO_SW)。该引脚应具有 20µF 的大容量输入电容。针对该电容建议的配置是采用两个并联的 10µF 电容器。此外,该引脚应连接到 VDDIO 引脚,并且两个引脚必须由相同的 3.3V 电源供电。如果需要,可以使用铁氧体磁珠进行隔离。