ZHCABZ5A November 2021 – December 2022 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1

4.3 放置元件

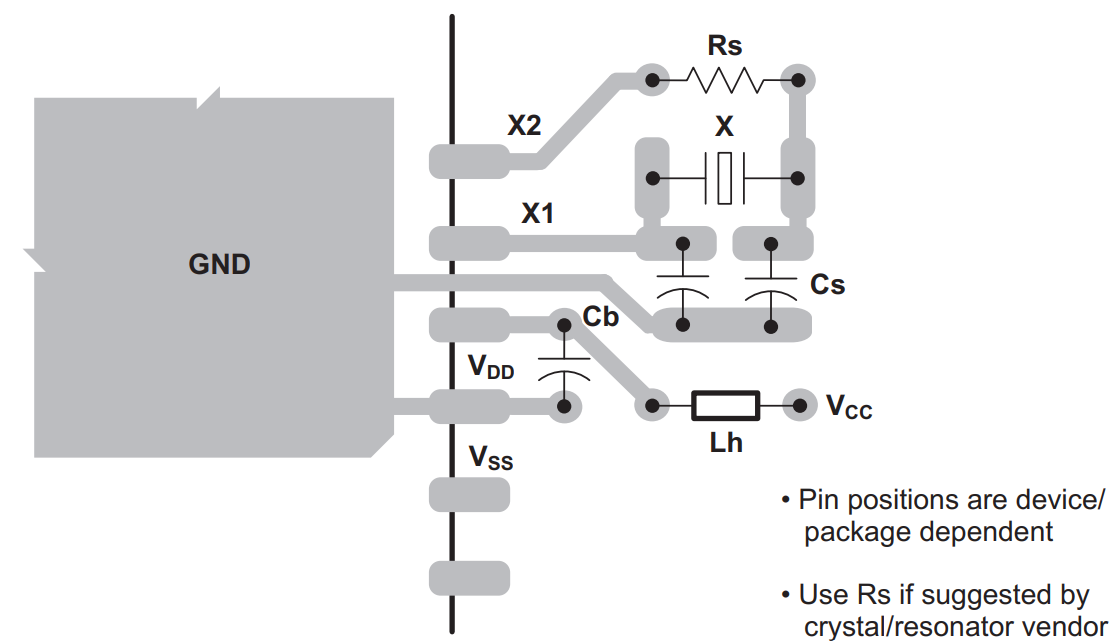

在电路板上确定 C2000芯片的位置之后,下一个应该放置的元件是晶体/振荡器。应将其放置在尽可能靠近器件的位置,以确保实现最有效的时钟解决方案。具体而言,到 X1/X2 的引线应尽可能短。根据所使用的特定晶体所需的额外元件,可以通过不同的方式在电路板上对晶体/谐振器进行布线。图 4-4 展示了一个示例,其中包含一个 2 层电路板和一个需要额外串联电阻器 Rs 的晶体。当进行器件间时钟迹线的布线时,可尝试使用3 W 间隔规则。时钟迹线的中心至任意邻近信号迹线中心的距离应至少为时钟迹线宽度的 3 倍。许多时钟,其中包括低频时钟,可具有很快的上升和下降时间。采用3 W 规则可削减迹线间的串扰。一般来说,器件间并行的走线之间也应当保持一定 的空间。避免采用直角来布置走线,以大大减少走线长度及阻抗的不连续性。要进一步保护器件不受串扰影响,尽可能地在时钟信号线旁侧布置保护迹线(GND 引脚至 GND 引脚)。这样可以减少时钟信号耦合。

图 4-4 建议的振荡器布局

图 4-4 建议的振荡器布局要放置的下一个最重要的元件是去耦/旁路电容器。这些电容器应尽可能靠近各自的引脚放置,从而进一步降低噪声并有助于确保器件的电源稳定。距离引脚超过一英寸的去耦电容器性能较差。另一方面,大容量电容器可放置在离芯片相对较远的位置,而不会对其性能产生重大影响。图 4-5 展示了良好的去耦电容器放置。

后面应该跟随的其它元件是 JTAG 接头/电路和 XRSn 电路。

对于使用 TMS320F28004x 器件上的内部 1.2V 直流/直流稳压器的系统,下面概述了确保正确设计直流/直流电路的关键指南。

- TI 建议将 VDDIO_SW 和 VDDIO 星型连接至相同的 3.3V 电源。

- 所有外部元件应尽可能靠近引脚放置。

- 由 VDDIO_SW、输入电容器 (CVDDIO_SW) 和 VSS_SW 形成的环路必须尽可能短。

- 反馈引线必须尽可能短,并且远离开关输出 (VSW) 等任何噪声源。

- 对于输入电容器 (CVDDIO_SW) 和 VSS_SW,需要在接地平面中实施单独的岛或切口。

- 建议使用 VDD 平面将 VDD 节点连接到 LVSW-CVDD 点,以最大程度地减小寄生电阻和电感。