ZHCABZ5A November 2021 – December 2022 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1

4.4 接地层

PCB 上的铜平面是出色的高频电容器,可与建议的电容器一起用于高频旁路。实心平面的另一个好处是它们可以充当良好的散热器,以降低过高的热水平。

如果电路板有足够多的层,那么一个良好的做法是在 PCB 上布置一个接地平面。该接地平面不仅有助于在电路板上路由接地信号,还有助于降低接地噪声。电路板上的每个信号都有一个返回电流(通过 GND),这可以确保返回路径通过阻抗最小的路径。对于在不同层上具有多个接地平面的电路板,采用过孔拼接来连接这些接地平面并进一步更大限度地降低阻抗非常有用。有关返回路径的更多信息,请参阅高速布局指南的返回电流和环路面积 部分。

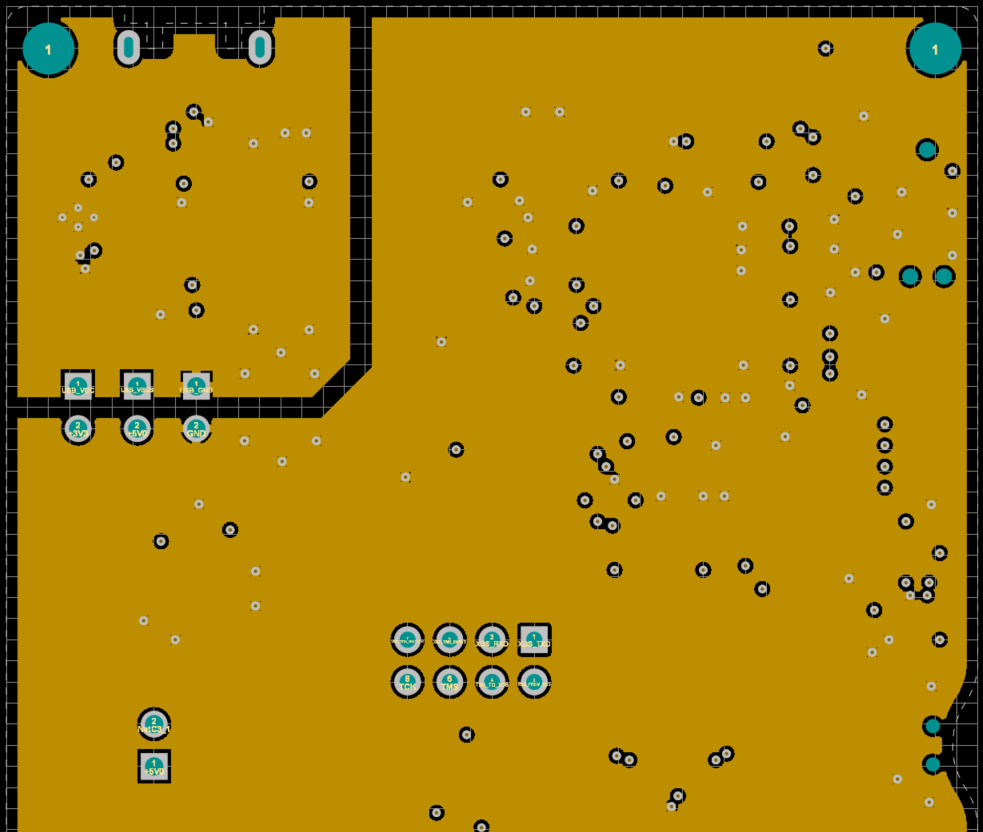

图 4-7 LaunchPad 上的接地平面

图 4-7 LaunchPad 上的接地平面实现有效接地平面的关键在于,确保该平面完好无损且在电路板的整个层上具有良好的连接。过孔和布线等板载连接会切碎接地层并降低其有效性。过孔会在电路板的多个层中形成一个孔,而布线会切断接地平面不同部分之间的连接。在下面的左图中,请注意 RGND 过孔只有一个到接地平面的连接,并且周围的接地孔连接非常细。此外,在图 4-8 中,请注意孔的左上角仅通过一条很细的铜片连接到覆铜的左下角。这两个图都展示了不良的接地平面。为确保接地平面的连接线粗或接地覆铜没有严重切碎,重新排列过孔和布线会很有帮助。

为某个层应用接地平面时,应检查该平面是否整层具有良好的连接。应重新设计缺少平面或连接线细的区域,从而更大限度增加接地平面面积。通常,这可以通过减少过孔数量和将多组布线彼此靠近布置来实现。在某些情况下,修改引脚复用选项和原理图对改进布线可能会有所帮助。有时,在布局布线过程开始之前,这些好处可能并不明显,但优化引脚复用可以缩短布线长度并减少过孔使用,从而实现更好的接地平面。