ZHCABZ5A November 2021 – December 2022 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1

3.3.3 内部与外部模拟基准

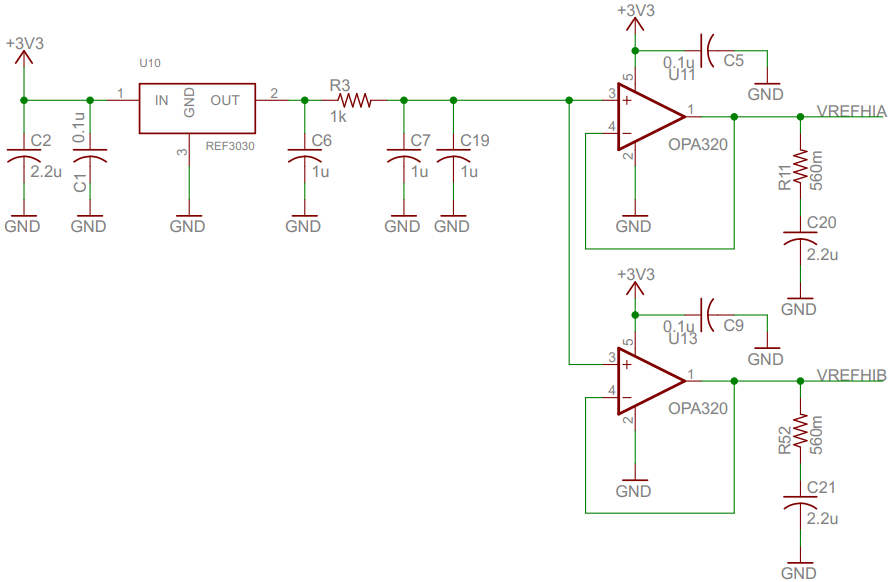

板载 ADC 使用 VREFHIx 和 VREFLOx 作为电压基准。对于大多数应用,内部电压基准可提供足够高的性能。因此,VREFHIx 引脚电压由内部带隙电压基准驱动,可以选择该电压基准的电压为 1.65V 输出(0V 至 3.3V)或 2.5V 输出(0V 至 2.5V)。如果所实施系统的设计要求更高的精度,则可以改用外部基准电压。

当使用内部基准模式时,不应在 VREFHI 引脚上放置额外的电压源,因为器件本身会将电压驱动到该引脚上。在外部基准模式下,使用 REF3030 和高速运算放大器等外部电路从外部驱动高基准电压引脚。该电压必须为 2.4V 至 VDDA。在所有情况下,确保在该引脚上放置一个 2.2µF 电容器。

图 3-7 外部模拟基准的基准电路

图 3-7 外部模拟基准的基准电路