ZHCACF7A june 2021 – march 2023 F28377D-SEP , TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

5.1 VREFLO 采样概念

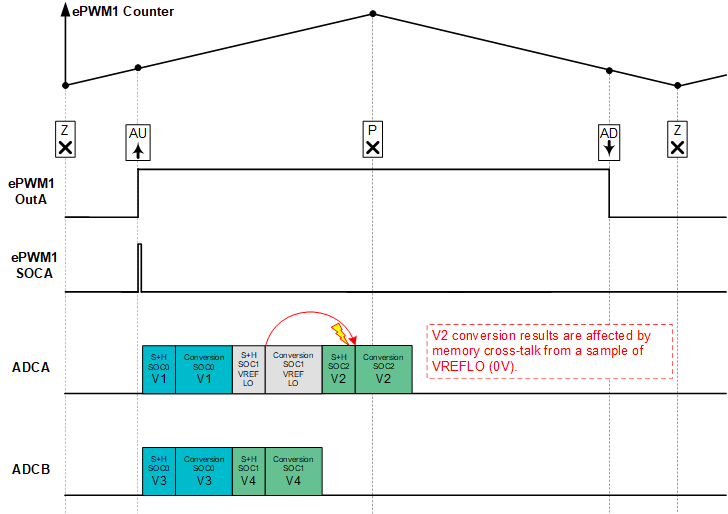

节 3.1中提供了一种对四个电压进行采样的示例系统。其中一个电压 V2 稳定性能较差(由于使用分压器直接驱动 ADC 输入而导致源阻抗过高)。图 5-1 展示了采样方案的一种可能重组方式,其中在相关通道之前添加了一个 VREFLO(零量程)样本。这样做的结果是将来自电压 V1 的存储器串扰(可在任何时间接受任何电压的独立信号)替换为来自 VREFLO 的存储器串扰(稳定地产生串扰而将 V2 恰好拉至 0V)。

图 5-1 VREFLO 采样方法的时序

图 5-1 VREFLO 采样方法的时序与单 ADC 方法不同,可以运用预采样 VREFLO 方法来处理同一 ADC 上的多个信号。这种方法仅受限于 ADC 包装器中可用于对额外转换进行排序的备用转换启动 (SOC) 结构数量(无需外部引脚)以及应用为处理 VREFLO 样本所能承受的额外延迟量。后面几节还将表明,对 ADC 结果进行轻度后处理也是可取的。执行此操作会增加一些额外的延迟,应用也需要吸收这些延迟。