ZHCACF7A june 2021 – march 2023 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

3.2 S+H 趋稳分析

如 C2000 ADC 的电荷共享驱动电路 中所述,可以使用 RC 趋稳模型确定所需稳定时间的近似值。模型的时间常数由以下公式给出:

所需的时间常数数量可通过以下公式得出:

因此,总 S+H 时间应设置为大约:

其中以下参数由器件特定数据手册中的 ADC 输入模型提供:

- n = ADC 分辨率(以位数表示)

- RON = ADC 采样开关电阻(以欧姆为单位)

- CH = ADC 采样电容(以 pF 为单位)

- CP = ADC 通道寄生输入电容(以 pF 为单位)

以下参数取决于应用设计:

- 稳定误差 = 可耐受的稳定误差(以 LSB 为单位)

- Rs = ADC 驱动电路源阻抗(以 Ω 为单位)

- CS = ADC 输入引脚上的电容(以 pF 为单位)

表 3-1 展示了使用 F280049 数据手册中的值和 CS 250pF 计算得出的稳定时间。Rs 设置为 7444Ω,这是由 1MΩ 和 7.5kΩ 电阻构成的分压器的有效阻抗 (1MΩ || 7.5kΩ)。

| 参数 | 示例 1 |

|---|---|

| CS | 250 pF |

| CH | 12.5pF |

| Cp | 10pF |

| Rs |

7444Ω |

| RON | 500Ω |

| n | 12 位 |

| 稳定误差 |

0.5LSB |

| τ | 1.96µs |

| k |

6.015 |

| 稳定时间 | 11.8µs |

此分析表明,要实现完整的 12 位稳定性能,需要 11.8μs 的稳定时间。遗憾的是,这远大于 F280049 器件中 ADC 可配置的最大 S+H 时间。此外,这甚至也长于 100kHz ePWM 触发源产生的 10μs 触发周期。如此长的 S+H 窗口所导致的延迟也可能对控制系统的性能产生非常不利的影响。总体而言,仅通过配置正确的 S+H 时间无法获得良好的稳定性能。

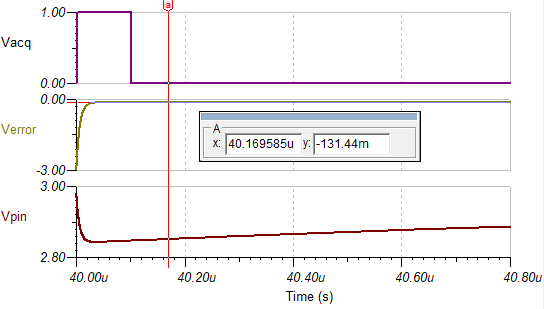

图 3-3 展示了将 S+H 时间设置为 100ns 时的图 3-2 仿真结果。这个时间远小于提供完整 12 位稳定性能预计所需的 11.8µs,但代表了在 100kHz 采样率和低延迟采样的情况下可以合理配置的时间。仿真展示了 100ns S+H 窗口后的稳定误差为 131mV,约为 ADC 3.0V 范围的 4%。考虑到理想的 12 位 ADC 能够解析 ADC 满量程范围大约 0.02% 的步进,这种性能非常差。

图 3-3 具有 100ns S+H 的 V2 电路的趋稳仿真

图 3-3 具有 100ns S+H 的 V2 电路的趋稳仿真