ZHCACF7A june 2021 – march 2023 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

4.1 专用 ADC 概念

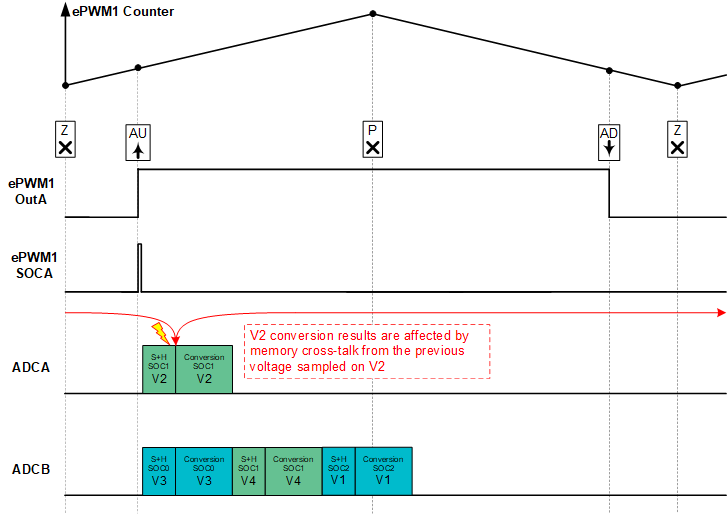

节 3.1 所示的系统中使用了两个 ADC 来对四个电压进行采样,其中只有一个电压具有较差的输入稳定性能(电压 V2)。为两个 ADC 中的每一个分配两个信号时,处理四个电压的总延迟最短。但是,如果采样方案如图 4-1 所示重新排列,那么稳定性能较差的信号(电压 V2)将收到一个专用的 ADC。

图 4-1 专用 ADC 方法的时序

图 4-1 专用 ADC 方法的时序将受影响的信号隔离到单个 ADC 的主要好处是,存储器串扰误差现在源自同一信号的先前采样值。如果信号移动速度不是很快,S+H 电路将以接近当前输入电压的值启动。这大大缩短了输入稳定所需的距离,从而实现可接受的稳定性能。但是,如果输入电压中出现较大的阶跃,ADC 可能需要多次采样,才能赶上输入端的新值。因此,专用 ADC 策略通常更适合慢速信号或直流输入信号。然而,即使在信号速度较快的情况下,存储器串扰效应至少会变得系统化,与从不相关信号耦合到相关信号的存储器误差相比,这通常是一种改进。

当然,使用专门的 ADC 对单个输入信号进行采样会增加应用中剩余信号的处理延迟。例如,如图 4-1 所示重新排列信号后,生成最终 ADC 结果的延迟增加了 50%!(假定所有转换均配置为使用 ADC 等量的时间来处理。)