ZHCACF7A june 2021 – march 2023 F28377D-SEP , TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

4.4 专用 ADC 电路的稳定性能仿真

节 4.2中就专用 ADC 设计对单输入步进的响应提供了一个简单的仿真。但是,仿真也可用于评估使用交流电源时的稳定性能。这样可以研究稳定性能如何随输入频率的增加而变化。

在继续之前,先查看以下 TI 高精度实验室视频中介绍的交流输入仿真方法可能会有用:最终 SAR ADC 驱动器仿真。

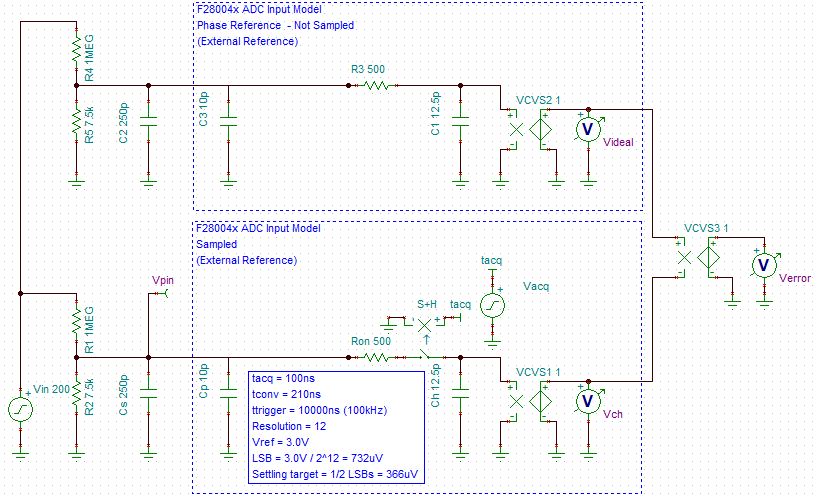

图 4-4 展示了交流仿真的仿真设置。400V 直流输入源已替换为 400Vpp 正弦输入。顶部添加了一个与原始电路一样但减去了采样部分的电路。这对于生成一个可与采样电压进行比较的参考波形是必要的。如果直接使用输入源进行比较,则来自各种 R-C 组件的相位延迟会掩盖稳定误差。

图 4-4 专用 ADC 的交流仿真原理图

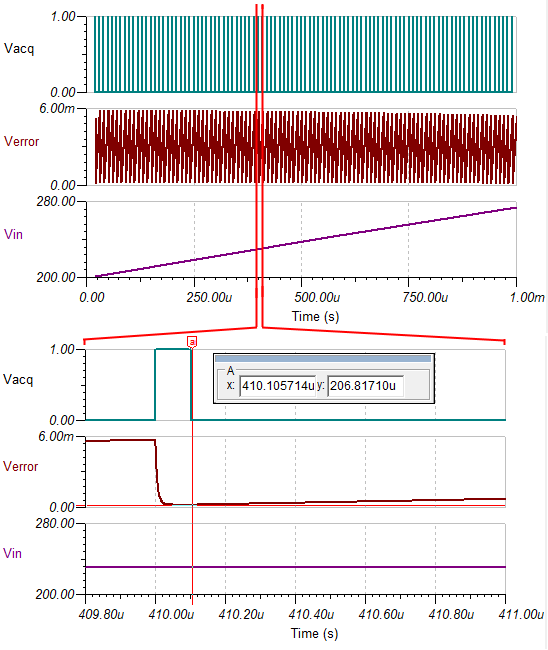

图 4-4 专用 ADC 的交流仿真原理图图 4-5 展示了在 1ms 内对许多样本进行 60Hz 交流输入仿真的结果。通过在正弦波上升时选择任意样本并检查误差波形,可以在 S+H 窗口结束时看到大约 0.2mV 的稳定误差。该稳定误差水平表示电路在 60Hz 输入条件下(3.0V 范围内的 1/2 LSB 为 0.37mV)实现了良好的稳定性能。

图 4-5 60Hz 交流输入的趋稳仿真

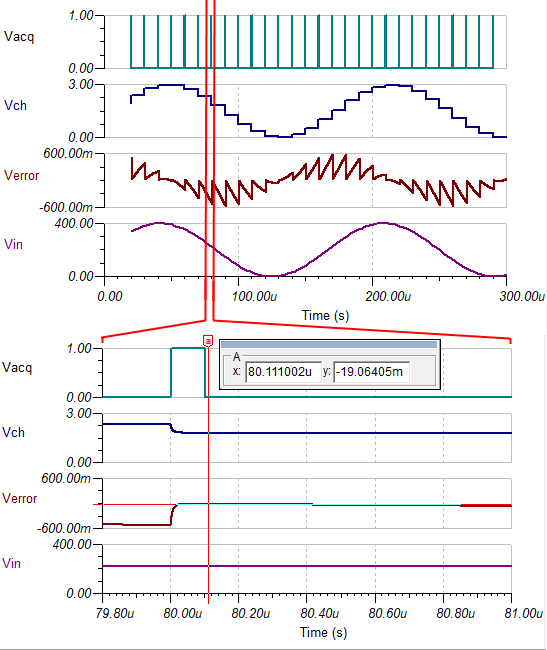

图 4-5 60Hz 交流输入的趋稳仿真与 60Hz 输入相比,图 4-6 展示了使用 6kHz 输入进行仿真的结果。在波形变小的同时,S+H 周期结束时的误差显示稳定误差约为 19mV,因此该电路在尝试跟踪更快的输入时表现不是很好。但请注意,增加外部 ADC 引脚电容 CS 可以提高较高速度时的稳定性能。需要注意的是,要确保 CS 不会太大,而导致 6kHz 输入会被由 CS 和 RS 组成的低通滤波器衰减。

图 4-6 6kHz 交流输入的趋稳仿真

图 4-6 6kHz 交流输入的趋稳仿真稳定误差除了会随着 ADC 输入频率的增加而增加外,其需要注意的另一个重要属性是,与信号的慢速部分相比,输入信号的快速部分会导致误差增加。因此,稳定误差不会同等地影响输入正弦波的所有部分,从而导致采样波形失真。