ZHCACF7A june 2021 – march 2023 F28377D-SEP , TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

3.4 问题总结

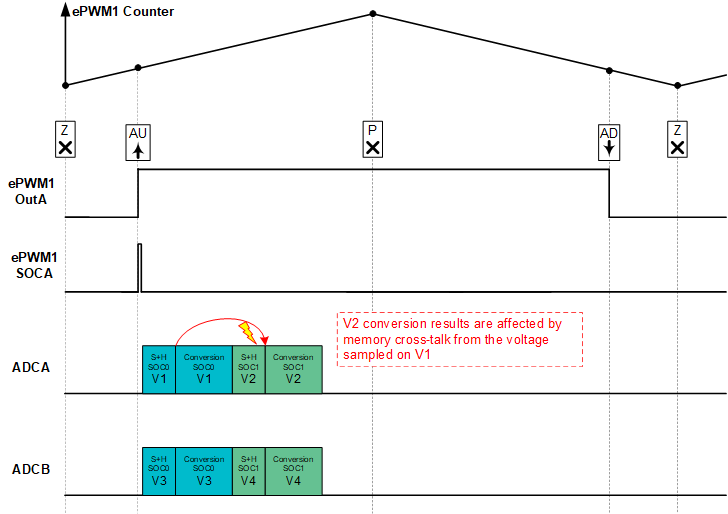

由于分压器具有较高的有效源阻抗并且该设计不使用运算放大器缓冲器来驱动 ADC 通道,因此电压 V2 将出现显著的 S+H 稳定误差。由于系统使用多路复用采样方案,在该方案中,ADCA 在每次收到触发信号时对 V2 之前的电压 V1 进行采样,因此该稳定误差将表现为从 V1 到 V2 的存储器串扰,如图 3-4 所示。这意味着当 V1 低于 V2 时,V2 的采样结果将被拉低,而当 V1 高于 V2 时,V2 的结果将被拉高。此外,如果 V1 和 V2 处于 ADC 输入范围的相反极端,则该误差的幅度预计约为 130mV(如图 3-3 中的仿真所示)。

图 3-4 示例系统存储器串扰

图 3-4 示例系统存储器串扰通常,由于系统对 V1 和 V2 独立的信号进行采样,V2 中引起的存储器串扰误差将不可预测地变化。这可能会导致系统性能不佳和不稳定。理想情况下,需要重新设计用于驱动 V2 的信号调节电路,以便确保良好的稳定性能,但由于额外的系统限制或使用固定的现有系统,这并非始终可行。节 4和节 5介绍了将存储器串扰误差转换为更系统性和更可预测形式的几种方法。