ZHCACF7A june 2021 – march 2023 F28377D-SEP , TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

5.5 讨论 VREFLO 采样序列

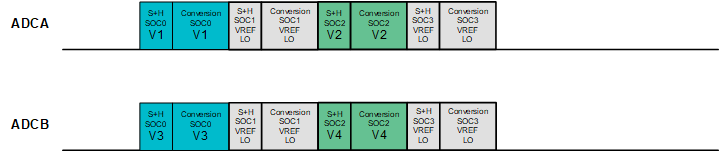

如节 5.1中所述,利用 VREFLO 采样方法来缓解存储器串扰问题适用于每个 ADC 处理多个信号的情况(与专用 ADC 方法不同)。在设置此采样序列时,需要考虑一些要点。这里将以图 5-3作为方案示例,其中四个信号分布到两个 ADC 上并都需要通过 VREFLO 采样从存储器串扰缓解中受益。

首先要考虑的是,即使每个序列中的最后一个 SOC (SCO3 = VREFLO) 不会在序列中的第一个采样(SOC0 = V1 或 V3)之前立即发生,但出于存储器串扰方面的考虑,由于采样的周期性质,该采样将影响序列中的第一次转换。因此,将 VREFLO 附加到序列末尾,并使受存储器串扰影响的通道成为序列中的第一个采样是一种可接受的配置。

此外,要考虑 ISR 的触发器应置于序列中的哪个位置。通常,序列中的最后一个 SOC 将触发 ISR,以便确保在 CPU 进入 ISR 时所有 ADC 结果都已准备就绪。但是,不需要读取 VREFLO 转换结果,因此 ISR 触发器的理想位置是 SOC2 之后,而不是 SOC3 之后。因此,即使两个信号都会从图 5-3中的 VREFLO 存储器串扰缓解中受益,但延迟也只会增加一个 VREFLO 采样所需的时间,而不是两个(序列结束时 VREFLO 转换的延迟可以被屏蔽)。

图 5-3 所有通道的 VREFLO 采样时序

图 5-3 所有通道的 VREFLO 采样时序