ZHCACF7A june 2021 – march 2023 F28377D-SEP , TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

5.2 VREFLO 采样方法误差的属性

对因 VREFLO 导致存储器串扰的电路进行仿真时,只需对 C2000 MCU 的 ADC 输入电路评估 中提供的标准 ADC 输入趋稳仿真进行极小的更改。默认设置已经强制施加正电压,而 S+H 电容器 CH 从 0V 的初始条件开始。

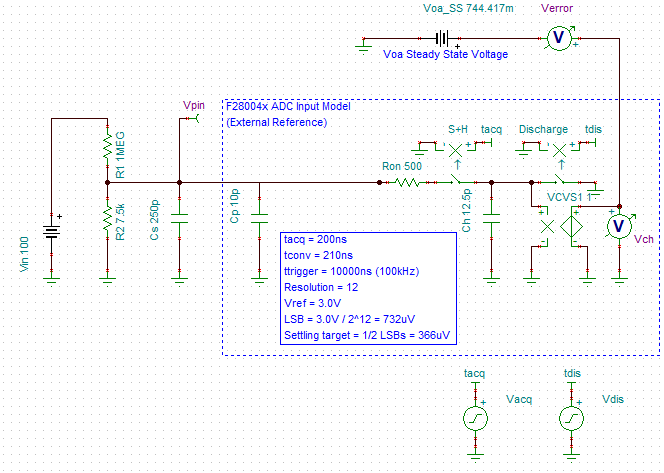

测量 VREFLO 稳定误差的仿真设置如图 5-2 所示。使用的 S+H 时间为 200ns。表 5-1 展示了针对某个输入电压范围仿真采样电压的结果。从最右侧的“采样电压误差 (%)”列可以看出,包括 VREFLO 串扰误差在内的采样电压表现为线性比例误差(增益误差)。

图 5-2 VREFLO 采样仿真原理图

图 5-2 VREFLO 采样仿真原理图| Vin | Vpin | 采样电压 | 采样电压误差 (%) |

|---|---|---|---|

| 400V | 2.978 | 2.853 | -4.39 |

| 300 V | 2.233 | 2.139 | -4.39 |

| 200V | 1.489 | 1.426 | -4.39 |

| 100V | 0.744 | 0.713 | -4.39 |