ZHCUBR5A October 2022 – February 2024

- 1

- 说明

- 资源

- 特性

- 应用

- 6

- 1 CLLLC 系统说明

- 2 CLLLC 系统概述

- 3 图腾柱 PFC 系统说明

- 4 重点产品

-

5 硬件、软件、测试要求和测试结果

- 5.1 所需的硬件和软件

- 5.2

测试和结果

- 5.2.1 测试设置(初始)

- 5.2.2 CLLLC 测试程序

- 5.2.3 TTPLPFC 测试程序

- 5.2.4 测试结果

- 6 设计文件

- 7 软件文件

- 8 相关文档

- 9 术语

- 10作者简介

- 11修订历史记录

5.2.2.3.1 设置实验 3 的软件选项

- 要运行该实验,请确保按前面部分(即图 5-7)所述设置硬件。请勿向电路板提供任何高压电源。

打开“<install Directory>\C2000Ware_DigitalPower_SDK_<version>\libraries\sfra\gui\CompDesigner.exe”

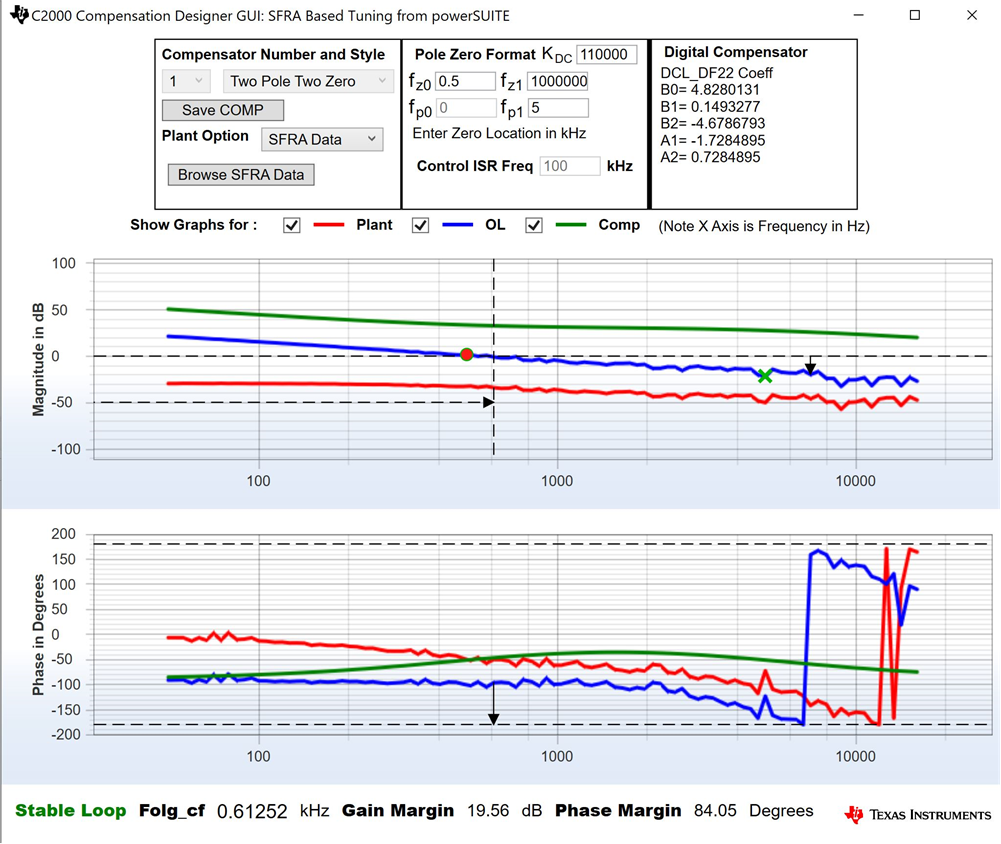

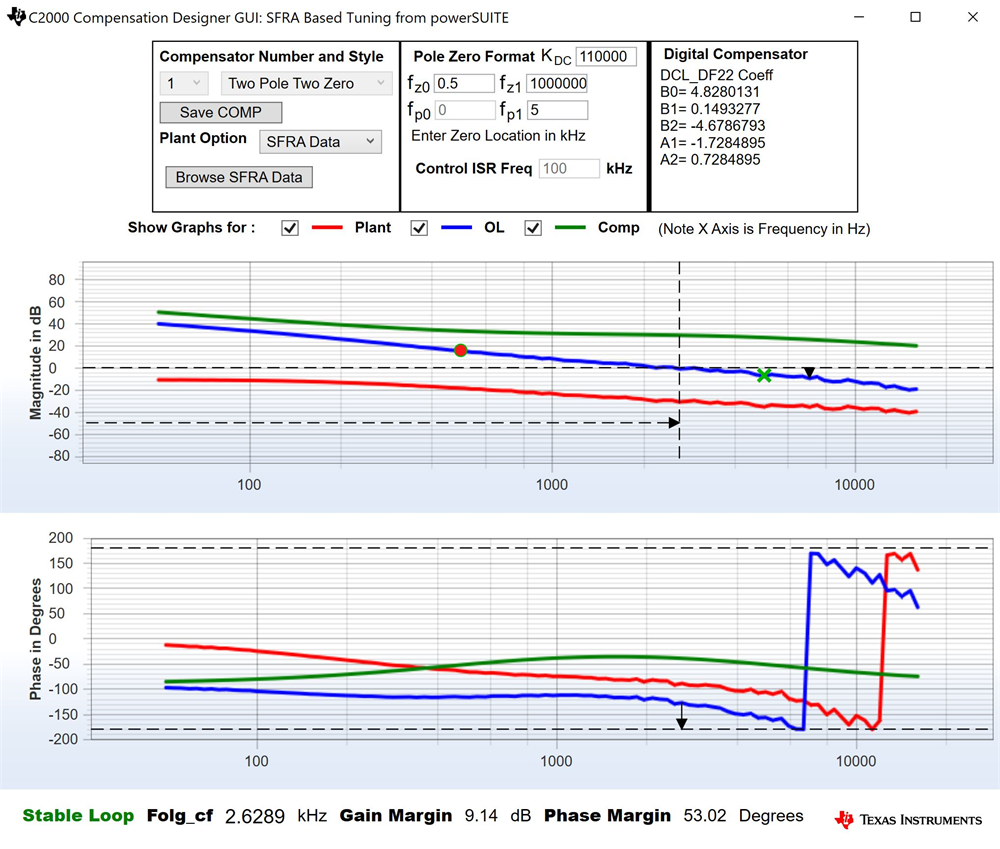

- 然后,补偿设计器将启动并提示用户选择有效的 SFRA 数据文件。将实验 1 中运行的 SFRA 数据导入补偿设计器来设计双极点、双零点补偿器。在该设计迭代过程中最好保持更大的裕度,以确保环路闭合时系统是稳定的。可以检查来自 SFRA 不同运行的受控体数据,以在所有条件下实现稳定的系统,例如,图 5-20 和图 5-21显示使用设计的补偿器在 500kHz 和 300kHz 下进行的两次运行是稳定的。

图 5-20 输出连接阻性负载时电压环路的补偿器设计(采用基于 SFRA 的受控体测量),含 500kHz 下的测量数据

图 5-20 输出连接阻性负载时电压环路的补偿器设计(采用基于 SFRA 的受控体测量),含 500kHz 下的测量数据 图 5-21 输出连接阻性负载时电压环路的补偿器设计(采用基于 SFRA 的受控体测量),含 333kHz 下的测量数据注:

图 5-21 输出连接阻性负载时电压环路的补偿器设计(采用基于 SFRA 的受控体测量),含 333kHz 下的测量数据注:调优以 DF22 方式执行;不过,我们在软件中运行 DF13。之所以这么做,是因为 DF13 软启动更容易,而 DF22 结构则无法实现软启动。两种情况下的系数是相同的。在编写本文档时,DCL 中不提供 DF12 结构。

- 对补偿器设计感到满意后,可以在 CLLLC_settings.h 文件中更新补偿器值。

- 关闭补偿设计器

- 在构建过程中,在 settings.h 文件中设置了以下定义。

#if CLLLC_LAB == 3 #define CLLLC_CONTROL_RUNNING_ON CLA_CORE #define CLLLC_POWER_FLOW CLLLC_POWER_FLOW_PRIM_SEC #define CLLLC_INCR_BUILD CLLLC_CLOSED_LOOP_BUILD #define CLLLC_CONTROL_MODE CLLLC_VOLTAGE_MODE #define CLLLC_TEST_SETUP CLLLC_TEST_SETUP_RES_LOAD #define CLLLC_PROTECTION CLLLC_PROTECTION_ENABLED #if CLLLC_SFRA_ALLOWED == 1 #define CLLLC_SFRA_TYPE CLLLC_SFRA_VOLTAGE #else #define CLLLC_SFRA_TYPE CLLLC_SFRA_DISABLED #endif #define CLLLC_SFRA_AMPLITUDE (float32_t)CLLLC_SFRA_INJECTION_AMPLITUDE_LEVEL1 #endif