ZHCUBR5A October 2022 – February 2024

- 1

- 说明

- 资源

- 特性

- 应用

- 6

- 1 CLLLC 系统说明

- 2 CLLLC 系统概述

- 3 图腾柱 PFC 系统说明

- 4 重点产品

-

5 硬件、软件、测试要求和测试结果

- 5.1 所需的硬件和软件

- 5.2

测试和结果

- 5.2.1 测试设置(初始)

- 5.2.2 CLLLC 测试程序

- 5.2.3 TTPLPFC 测试程序

- 5.2.4 测试结果

- 6 设计文件

- 7 软件文件

- 8 相关文档

- 9 术语

- 10作者简介

- 11修订历史记录

5.1.2.2 工程结构

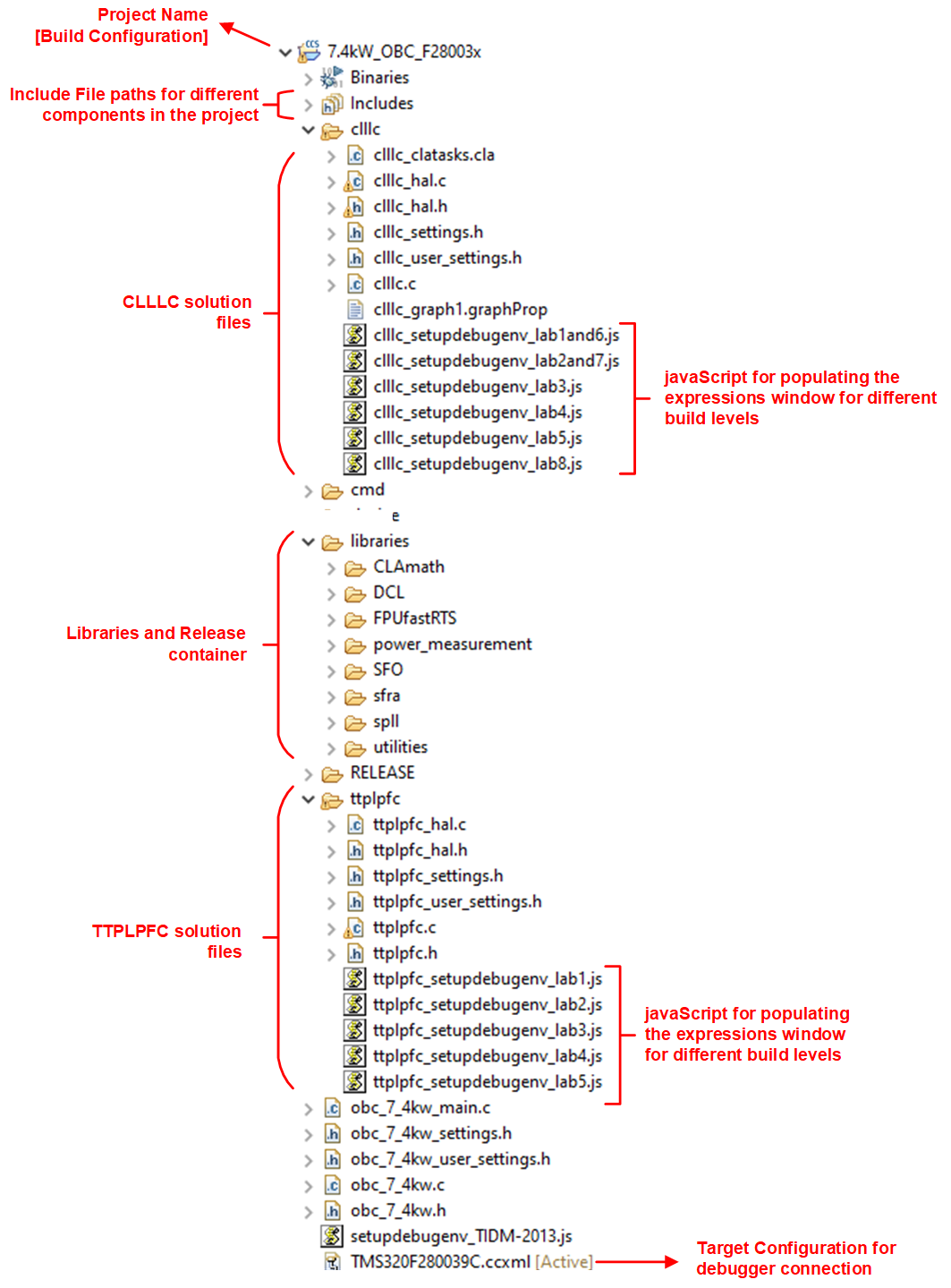

图 5-4 工程结构概览

图 5-4 工程结构概览图 5-4 展示了工程的总体结构。导入工程后,CCS 中将显示 Project Explorer,如图 5-5 所示。

<solution>.c/h 中包含特定于解决方案并且独立于器件的文件,其中含有核心算法代码。例如 TTPLPFC.c 或 CLLLC.h。

<solution>_hal.c/h 中包含特定于电路板和特定于器件的文件。该文件由特定于器件的驱动程序组成,以用于运行解决方案。如果用户想要使用不同的调制方案或不同的器件,除了更改工程中的器件支持文件,用户只需要对这些文件进行更改。

<solution>-main.c 文件包含工程的主要框架。该文件由对电路板和解决方案文件的调用(有助于构建系统框架)以及中断服务例程 (ISR) 和慢速后台任务组成。

对于该设计,有三个 <solution> 名字对象,即 obc_7_4kw、clllc 和 ttplpfc。请注意,为了保持最大的灵活性,我们已选择使 CLLLC 代码库和 TTPLPFC 代码库尽可能保持独立,而在需要包含独立于 TTPLPFC 和 CLLLC 的设置时添加了 obc_7_4kw 文件。这使最终用户能够独立操作每个级,并根据需要在其最终设计中为 PFC 或直流/直流级轻松整合不同的拓扑。

<solution>_settings.h 文件包含代码配置设置,例如要构建哪个实验。而 <solution>_user_settings.h 包含板级配置,例如 ADC 映射、GPIO 等的 #define。

solution.js 文件包含一个脚本文件,该文件可以在执行每个实验期间帮助将相关变量填充到观测器中。要使用这些脚本,请打开脚本控制台(“View”-“Scripting Console”)。将 solution.js 文件的内容粘贴到脚本控制台中,然后按 Enter。这将填充表达式窗口以供稍后调试。

解决方案名称也用作解决方案中使用的所有变量和定义的模块名称。因此,所有变量和函数调用都以 CLLLC 名称作为前缀(例如 CLLLC_vSecSensed_pu)。这种命名规则使用户组合不同的解决方案,同时避免命名冲突。

图 5-5 CLLLC 工程的 Project Explorer 视图

图 5-5 CLLLC 工程的 Project Explorer 视图OBC 工程由在 2 个内核(C28x 内核和 CLA 内核)上运行的三个 ISR(ISR1、ISR2 和 ISR3)组成。通过对 ISR1 触发器使用 ePWM,对 ISR2 触发器使用 eCAP,对 ISR3 触发器使用 ADC,可以完全通过硬件来控制 ISR 优先级。表 5-4 展示了每个 ISR 的分区方式及其任务。

| ISR | 触发源 | C28x | CLA |

|---|---|---|---|

| ISR1 (120kHz) | ePWM | 不适用 | 更新 CLLLC PWM 值 |

| ISR2 (120kHz) | eCAP | PFC 电流环路 | CLLLC 控制代码,启用 ISR1 |

| ISR3 (10kHz) | ADC | PFC 电压环路,仪表 | 不适用 |

ISR1 是为 PWM 更新保留的速度最快且不可嵌套的 ISR,完全在 CLA 上运行。ISR1 由 PRIM_LEG1_PWM_BASE → EPWM_INT_TBCTR_U_CMPC 事件触发。通常,可以通过向 CMPC 写入一个值来禁用该中断,该值大于 PRIM_LEG1_PWM_BASE 的所有可能的 TBPRD 寄存器值。这是通过 CLLLC_HAL_setupISR1Trigger 函数完成的。以下是与该 ISR 相关的定义。

#define CLLLC_ISR1_PERIPHERAL_TRIG_BASE CLLLC_PRIM_LEG1_PWM_BASE

#define CLLLC_ISR1_TRIG INT_EPWM1

#define CLLLC_ISR1_PIE_GROUP INTERRUPT_ACK_GROUP3

#define CLLLC_ISR1_TRIG_CLA CLA_TRIGGER_EPWM1INTISR2 被拆分到两个内核上。这样便可以对 TTPLPFC 和 CLLLC 代码进行简单的模块化代码隔离。在 C28x 上运行的 ISR2 和在 CLA 上运行的 ISR2 均由同一个源触发并协同运行。C28x 内核运行与 TTPLPFC 相关的任务,而 CLA 内核运行与 CLLLC 执行相关的任务。

ISR2 负责在需要 ISR1 时通过对 CMPC 进行写入以写入有效值来触发 ISR1。(注意:为了实现这一点,CMPC 未绑定到全局加载机制。此外,CMPC 的影子加载被禁用。)可以调整 CMPC 值以从 ISR1 获取所需的时序。每次启用 ISR1 时,都会将其触发两次。在第一个 ISR1 中,PWM 寄存器被更新,同步被启用。在第二个 ISR1 中,PWM 同步被禁用,CMPC 被设置为一个适当的值,使得 ISR1 不会再次触发。为简单起见,软件图和结构仅显示首次触发的 ISR1。

ISR2 以 ISR2_FREQUENCY 定期触发。一个备用 CAP 模块用于生成时基并触发中断。一个备用 ePWM 模块也配置有相同的时基,用于触发 ADC 转换。ISR2 负责运行控制律和计算 PWM 所需的时钟周期。影子寄存器写入完成后,ISR2 通过向 CMPC 寄存器写入一个有效值(即一个小于当前 TBPRD 寄存器的值)来启用 ISR1 触发器。ISR2 有 ISR2_primToSecPowerFlow 和 ISR2_secToPrimPowerFlow 两个变体,一个用于从初级侧到次级侧的功率流,另一个用于次级侧到初级侧的功率流。这样做是为了在控制不同方向的功率流时优化 CPU 周期。为了方便说明,这两者均在各自的实验中被称为 ISR2。根据时序,ISR1 可能会嵌套 ISR2 以进行更新写入,这些写入是时序关键型操作。以下是与该 ISR 相关的定义。

#define CLLLC_ISR2_ECAP_BASE ECAP1_BASE

#define CLLLC_ISR2_PWM_BASE EPWM5_BASE

#define CLLLC_ISR2_TRIG INT_ECAP1

#define CLLLC_ISR2_PIE_GROUP INTERRUPT_ACK_GROUP4#define CLLLC_ISR2_TRIG_CLA CLA_TRIGGER_ADCA2ISR3 完全在 C28x 内核上运行并由 ADCINT2 触发。ADCINT2 由使用 CPU 计时器启动的转换启动。它用于运行 TTPLPFC 的电压环路以及通用功能,例如对电流和电压信号执行连续均值计算以消除噪声。甚至为命令基准运行压摆率功能。

#define CLLLC_ISR3_TIMEBASE CLLLC_TASKC_CPUTIMER_BASE

#define CLLLC_ISR3_PERIPHERAL_TRIG_BASE ADCC_BASE

#define CLLLC_ISR3_TRIG INT_ADCC2#define CLLLC_ISR3_PIE_GROUP INTERRUPT_ACK_GROUP10这样就可以轻松地嵌套中断。图 5-6 展示了发生的三个中断的嵌套。该图像是通过监视窗口在周期变化启动时在开环中获取的,因此仅观察到一次 ISR1 触发。对于闭环系统,一个控制 ISR 周期到另一个控制 ISR 周期的时长变化很小,因此 ISR1 将被重复触发。

图 5-6 三级嵌套 ISR

图 5-6 三级嵌套 ISR另外,CPU 计时器用于触发慢速后台任务(这些任务均不由中断驱动,而是采用轮询方式)。

“A”任务在 TASKA_FREQ(即 100Hz)时触发。必须以此速率调用 SFRA GUI。以这一速率执行一个任务 A1。

“B”任务在 TASKB_FREQ(即 10Hz)时触发。这些任务用于一些基本的 LED 切换和不是时间关键型的状态机项目。这为三个任务(B1、B2、B3)提供服务;因此,每个任务的执行速率为 3.33Hz。

#define TASKA_FREQ 100

#define TASKB_FREQ 10该参考设计的软件被组织到按解决方案分隔的实验中,每个实验具有增量构建 (INCR_BUILD)。这些测试简化了系统启动和设计。

CLLLC 实验

实验 1:初级到次级功率流,开环检查 PWM 驱动器,未向电路板施加高功率。请参阅节 5.2.2.1

实验 2:初级到次级功率流,开环检查 PWM 驱动器和 ADC,具有保护功能,次级连接阻性负载。请参阅节 5.2.2.2

实验 3:初级到次级功率流,闭合电压环路检查,次级连接阻性负载。请参阅节 5.2.2.3

实验 4:初级到次级功率流,闭合电流环路检查,次级连接阻性负载。请参阅节 5.2.2.4

实验 5:初级到次级功率流,闭合电流环路检查,次级连接与电压源并联的阻性负载,以模拟次级侧的电池连接。请参阅节 5.2.2.5

这些定义位于“settings.h”文件中,可以直接在该文件中更改这些定义。