ZHCADN6 January 2024 AM67 , AM67A , AM68 , AM68A , AM69 , AM69A , DRA821U , DRA821U-Q1 , DRA829J , DRA829J-Q1 , DRA829V , DRA829V-Q1 , TDA4AEN-Q1 , TDA4AH-Q1 , TDA4AL-Q1 , TDA4AP-Q1 , TDA4APE-Q1 , TDA4VE-Q1 , TDA4VEN-Q1 , TDA4VH-Q1 , TDA4VL-Q1 , TDA4VM , TDA4VM-Q1 , TDA4VP-Q1 , TDA4VPE-Q1

1.3 Jacinto 7 UART 功能简介

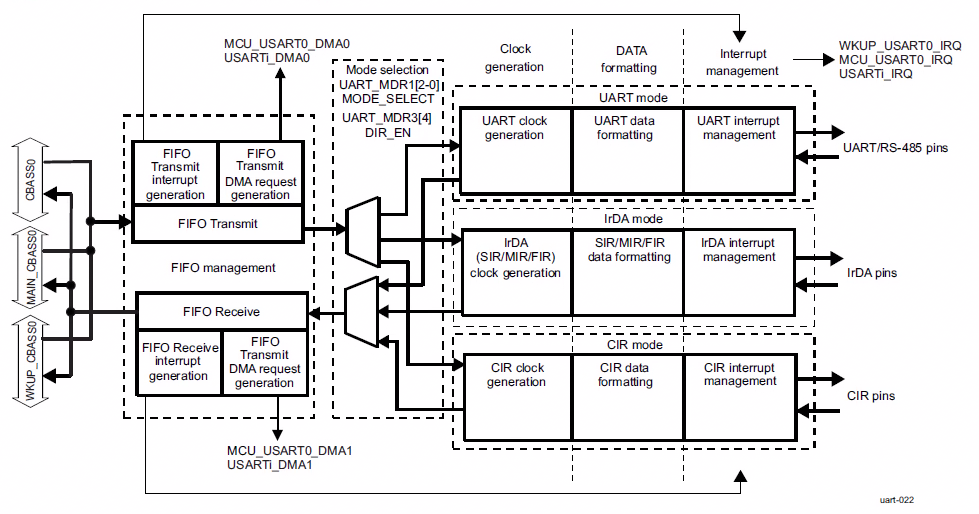

图 1-1 显示了 Jacinto 7 UART 功能方框图。当处理器需要发送数据时,只需要通过 CPU/DMA 将输出数据写入 FIFO。然后,数据通过 UART_THR 寄存器自动传输到 TX 引脚,并转换为 TTL 电平。如果 UART_THR 寄存器为空,则数据传输完成。在数据接收过程中,TTL 电平首先通过引脚转换为位数据,并由 UART_RHR 写入 FIFO。当 FIFO 达到阈值(最大 64 字节)时,将触发 CPU/DMA 中断,以将数据写入存储器。当读取足够的数据并且 FIFO 中的数据低于阈值时,中断条件将消失,数据接收完成。

图 1-1 UART 功能方框图

图 1-1 UART 功能方框图