ZHCAC41 February 2023 TMS320F280025C

2.3.1 同步输出信号

CLB 生成的输出信号很可能由 CLB 逻辑块中的不同逻辑块生成。这会导致每个输出信号中存在不同的延迟路径。为了更大限度地增加接收器件的建立时间和保持时间,可以使用总线时钟和简单的触发器使不同的 CLB 输出互相同步,请参阅#GUID-95B40206-ED42-415F-A721-7AAB915ACEC6。可使用 CLB 逻辑块中的有限状态机 (FSM) 块来实施触发器。但是,由于 CLB 逻辑块资源有限,最好仅在绝对需要时才使用此选项。

图 2-1 使用 D 类触发器同步输出

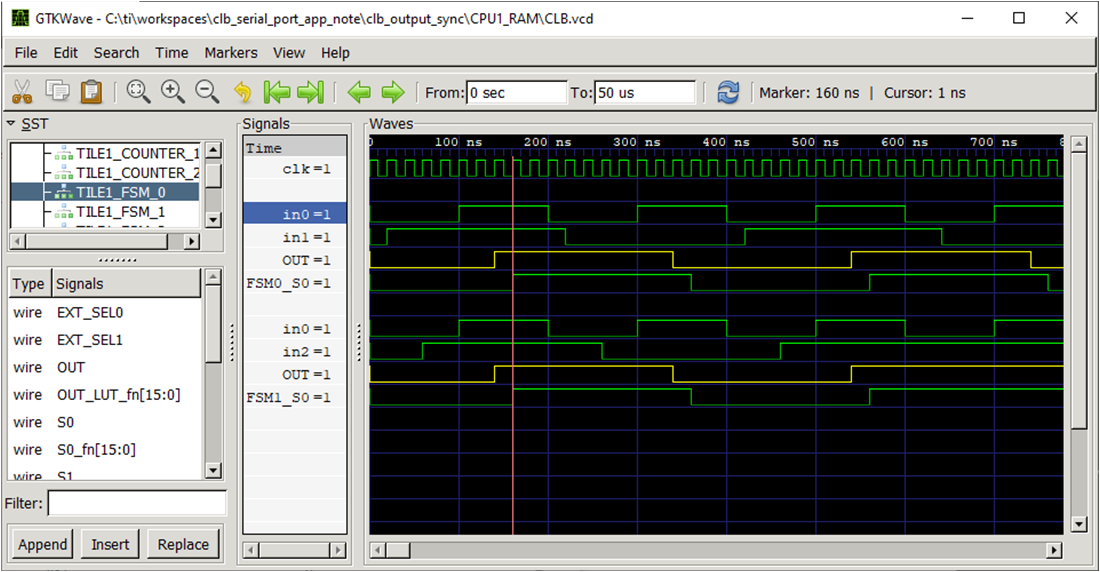

举个需要同步逻辑的例子,请考虑#FIG_OSN_VWC_3VB 中的仿真,其中显示了两个输入(in1 和 in2),它们在稍微不同的时间改变状态。这两个信号使用第三个“时钟”信号彼此同步,in0 使用的两个边沿触发 D 类触发器通过两个 FSM 来实施。从仿真中可以看出,每个 FSM 使用“时钟”信号 in0 锁存并延迟其输入信号。因此,两个 FSM 输出相互同步。

图 2-2 使用 FSM D 类触发器同步输出

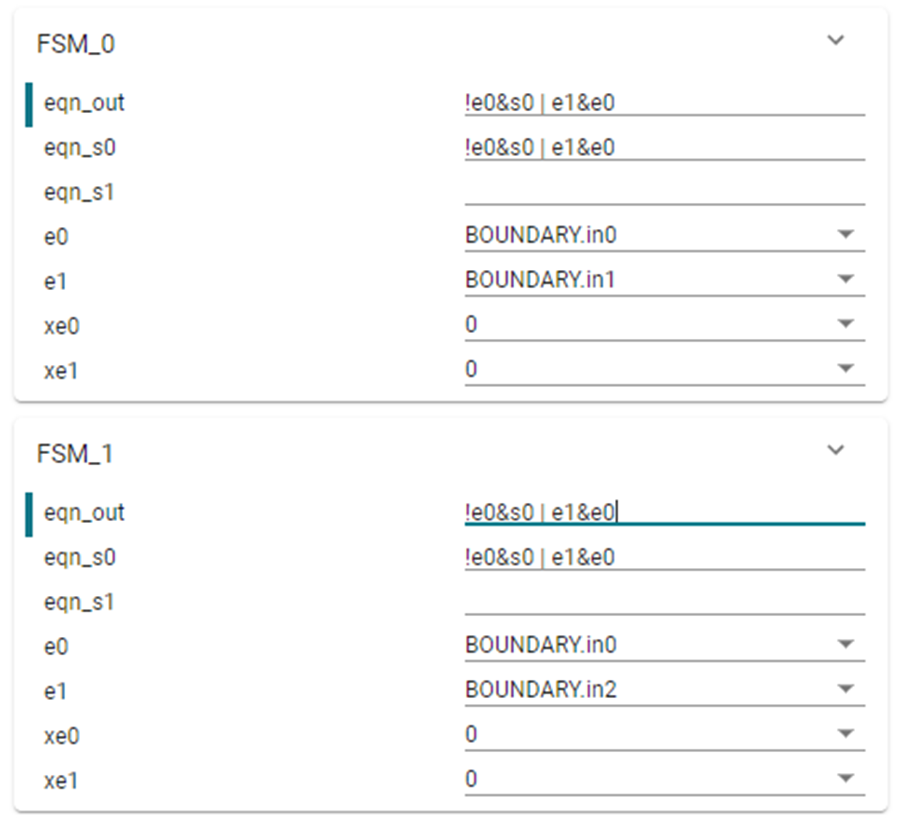

图 2-2 使用 FSM D 类触发器同步输出#FIG_RSC_5Y2_2VB 中显示了每个 FSM 输出和状态变量的逻辑方程。请注意,FSM out 和 s0 均设置为相同的方程,并且任一信号均可用于驱动最终输出。由于 out 是纯组合输出,而 s0 始终在下一个 CLB 时钟周期更新,因此两个信号之间存在 1 周期延迟。另请注意,在此仿真中,为同步上升沿检测设置 in0 输入滤波器。

图 2-3 D 类触发器的 FSM 设置

图 2-3 D 类触发器的 FSM 设置