ZHCAC41 February 2023 TMS320F280025C

3.7.3 测试输出建立时间和保持时间

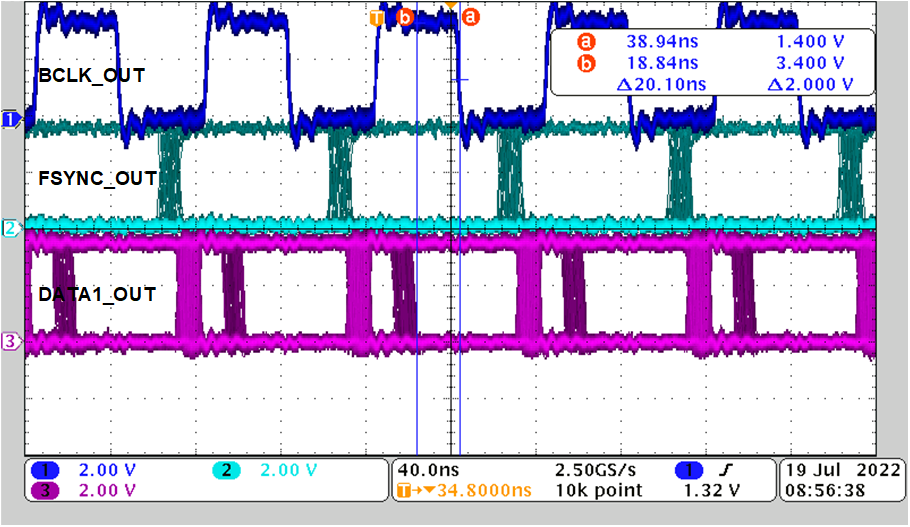

来自 CLB 的输出 TDM 流中的一个关键考虑因素是接收器件看到的预期建立时间和保持时间。为了测量建立时间和保持时间,使用一个示波器来持续捕获 CLB 的输出。#GUID-44D57C63-7D6E-4208-BA22-2911E1616CAE 显示了未将锁存和延迟逻辑添加到 FSYNC_OUT 和 DATA1_OUT 信号的 TDM 输出。由于 DATA1_OUT 信号中存在延迟,相对于 BCLK_OUT,DATA1_OUT 的建立时间和保持时间会减少。

图 3-15 无锁存和延迟逻辑的 TDM-8 输出

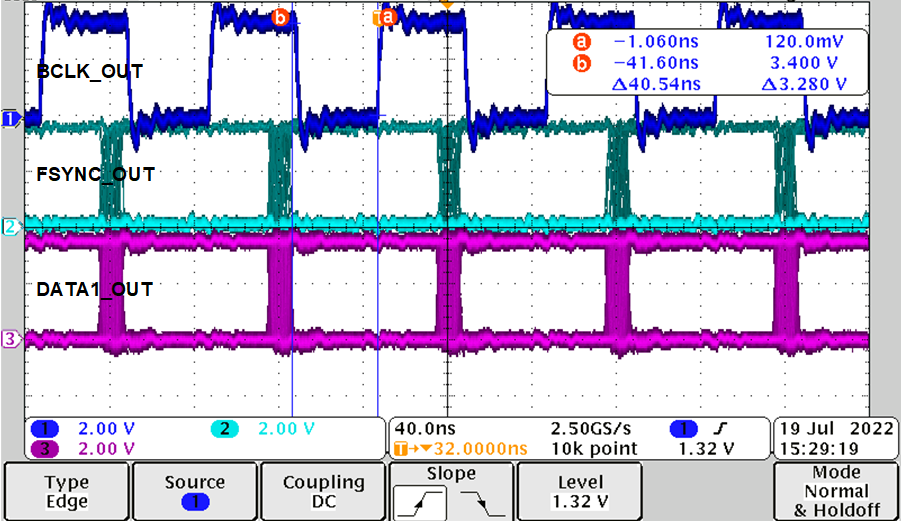

图 3-15 无锁存和延迟逻辑的 TDM-8 输出#GUID-E0F59FE5-F1A1-4126-8B31-E83AE0F3F4A3 中显示的示波器图显示了最终的 TDM 输出,其中的锁存和延迟逻辑已添加到 FSYNC_OUT 和 DATA1_OUT 信号中。使用这种方法可以大大改善建立时间和保持时间。

图 3-16 最终 TDM-8 输出

图 3-16 最终 TDM-8 输出由于 BCLK_OUT 必须在没有抖动的情况下通过 CLB 逻辑块传递,因此在未对 BCLK_OUT 引入抖动的情况下无法准确控制 BCLK_OUT 和其他两个信号之间的时序。但在这种情况下,建立时间和保持时间是可以接受的。如果需要,可以使用 CLB 逻辑块中的 AOC 反转 BCLK_OUT 信号,以换取建立时间和保持时间。

最后请注意 FSYNC_OUT 和 DATA1_OUT 信号上的 10ns 抖动。这是由于 CLB 逻辑块以 100MHz 的频率对传入的 BCLK_IN 信号进行采样所致。抖动进一步缩短了建立时间和保持时间。