ZHCAB59B June 2019 – November 2020 TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

8.1.1 使用“Expressions”(表达式)窗口

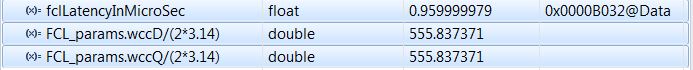

在此构建级别和后续构建级别运行电机时,请在“Expressions”(表达式)窗口中观察变量 fclLatencyInMicroSec。

图 8-2 显示了“Expressions”(表达式)窗口的快照。

图 8-2 “Expressions”(表达式)窗口延迟快照

图 8-2 “Expressions”(表达式)窗口延迟快照此变量指示在反馈采样和 PWM 更新之间经过的时间长度。经过时间(或延迟)是根据 PWM 更新后 EPWM 计时器立即开始的计数计算得出的。此处显示的值比实际更新时间长几个时钟周期。将 runMotor 标志设置为 MOTOR_RUN 并且电机开始运行后,由于代码中的初始设置,延迟时间会立即显示为大约 1.25µs。此延迟大小是在占空比适中时发生的,因此可以接受。在此时间段之后,可以通过将 fclClrCntr 设置为 1 来刷新延迟时间。不管 SAMPLING_METHOD 是多少,对于给定的 FCL_CNTLR,延迟都保持不变。当 FCL_CNTLR 为 PI_CNTLR 时,延迟约为 0.96µs,相比之下,设置为 CMPLX_CNTLR 时延迟为 0.98µs(请参阅以下注意事项)。

- 通过使用代码内联和其他优化技术,可以将这些时间进一步减小约 0.1µs 的区间。由于评估代码为库格式,因此有一定的开销。

- 为确保采集到更清晰的信号,ADC 的采样窗口保持足够的宽度。根据电路板布局布线和馈入 ADC 通道的电路的不同,可以将这个时间窗口减小近 60%。