SPRUJ64 September 2022

- Abstract

- Trademarks

- 1Key Features

- 2AM64x SKEVM Overview

- 3Functional Block Diagram

-

4System Description

- 4.1 Clocking

- 4.2 Reset

- 4.3 Power Requirements

- 4.4 Configuration

- 4.5 JTAG

- 4.6 Test Automation

- 4.7 UART Interface

- 4.8 Memory Interfaces

- 4.9 Ethernet Interface

- 4.10 USB 3.0 Interface

- 4.11 PRU Connector

- 4.12 User Expansion Connector

- 4.13 MCU Connector

- 4.14 Interrupt

- 4.15 I2C Interface

- 4.16 IO Expander (GPIOs)

- 5Known Issues and Modifications

- 6Revision History

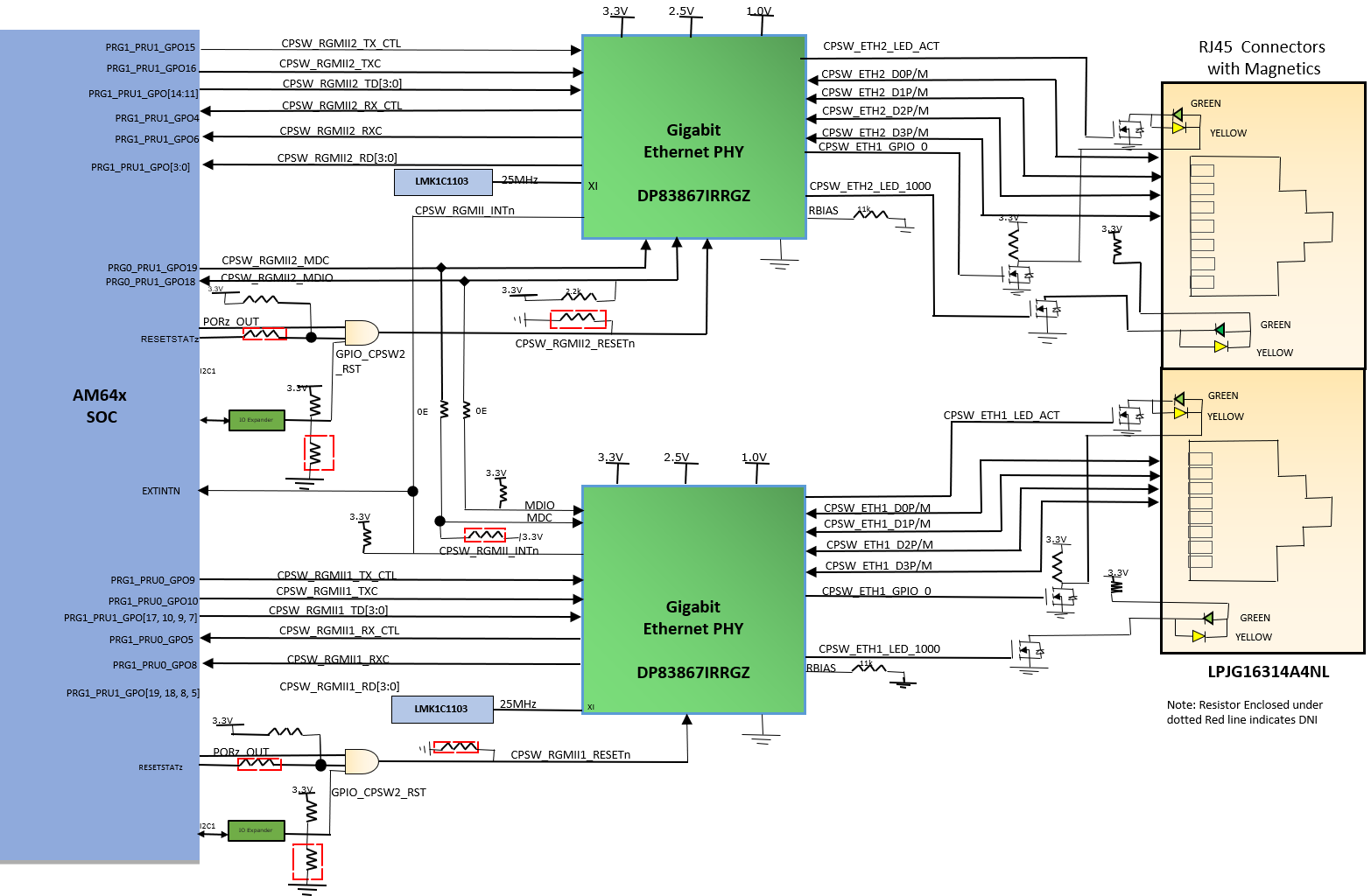

4.9.2 DP83867 – Power, Clock, Reset, Interrupt, and LEDs

The PHY devices include integrated MDI termination resistors. Thus, external termination is not provided.

Power: the RGMII signals from PRG0 and PRG1 domain are at 3.3-V IO level. The Gigabit PHY device DP83867 requires I/O power of 3.3 V and analog supply of 2.5 V and 1.0 V

Clock: A 25-MHz LVCMOS clock is given to the PHYs through clock buffer LMK1C1103 (individual outputs).

Reset: The reset for PHYs is from a circuit that ANDs the PORz_OUT and GPIO from IO expander and an optional RESETSTATz from the SoC. By default, RESETSTATz is not used for resetting the PHY. The IO expander is controlled through the I2C1 port of the AM64x SOC. Footprints for both a pull-up and a pull-down resistor are provided to the GPIO to set the default value. Each of the Ethernet PHYs have separate Reset Signals driven by GPIOs. A hardware reset is accomplished by applying a low pulse, with a duration of at least 1 micro-second to the RESET_N pin.

Interrupt: The interrupt from two CPSW RGMII PHYs from the PRG1 domain are tied together and is connected to the EXTINTN pin of AM64x SOC.

Four configurable LED pins and two GPIO of Ethernet PHY are used to indicate link status. Several functions can be multiplexed onto the LEDs for different modes of operation. The LED operation mode can be selected using the LEDCR1 register address 0x0018 on the DP83867 device. The default configuration are as follows.

LED0: By default, this pin indicates that a link is established. Additional functionality is configurable via LEDCR1 [3:0] register bits in the DP83867 device. LDE0 is not used in the CPSW PHY (DP83867), this is also a strap pin which is used to set mirror enable. Because these features are not required, the strapping for the LED0 is not provided.

LED_1: By default, this pin indicates that the 1000BASE-T link is established. This setting can be changed to auto negotiate to 10/100Mbps using the strap resistors. Additional functionality is configurable through the LEDCR1 [7:4] register bits in the DP83867 device. LED_1 is a also an strap pin which has an internal pull-down resistor to set the RGMII TX clock skew in the DP83867 device. Because this pin is set to active on both devices, this results in dim LED lighting when the LED is driven directly. Thus, a MOSFET is used to drive the LED, as shown in Figure 4-15.

LED_2: By default, this pin indicates receive or transmit activity. Additional functionality is configurable through the LEDCR1 [11:18] register bits in the DP83867 device. LED_2 is also a strap pin, which has an internal pull-down resistor to set the RGMII TX clock skew in the DP83867 device. The default condition is to auto negotiate and advertise the link as 10/100/1000Mbps, and this can be changed using the strap resistors provided. The pull up resistor is used for strap setting results in dim LED lighting when the LED is driven directly. Thus, a MOSFET is used to drive the LED, as shown in Figure 4-15.

GPIO0: In the DP83867 PHY, the GPIO can be configured to function as LED3 through the GPIO Mux Control Register 1 (GPIO_MUX_CTRL1), and the LED configuration can be set by programming the LEDCR1 register; this pin is used to indicate operation as a 100-Mbps connection. A MOSFET is used to drive the LED, as shown in Figure 4-15.

GPIO1: In the DP83867 PHY, the GPIO can be configured to function as LED3 through the GPIO Mux Control Register 1 (GPIO_MUX_CTRL1), and the LED configuration can be set by programming the LEDCR1 register, This is also a strap pin, which is used to set fast link drop (FDP); currently this is disabled.

LED indication in Ethernet RJ45 Connector: LED control is achieved through an external MOSFET.

RJ45 Connector LED Indication - CPSW (DP83867): LED1 is connected to RJ45 LED (Green) to indicate a 10/100 or 1000-MHz link, and LED2 is connected to RJ45 LED (Green) to indicate transmit/receive activity.

LED Control is achieved through an external MOSFET.

Figure 4-15 Ethernet Interface

Figure 4-15 Ethernet Interface