SPRUJ64 September 2022

- Abstract

- Trademarks

- 1Key Features

- 2AM64x SKEVM Overview

- 3Functional Block Diagram

-

4System Description

- 4.1 Clocking

- 4.2 Reset

- 4.3 Power Requirements

- 4.4 Configuration

- 4.5 JTAG

- 4.6 Test Automation

- 4.7 UART Interface

- 4.8 Memory Interfaces

- 4.9 Ethernet Interface

- 4.10 USB 3.0 Interface

- 4.11 PRU Connector

- 4.12 User Expansion Connector

- 4.13 MCU Connector

- 4.14 Interrupt

- 4.15 I2C Interface

- 4.16 IO Expander (GPIOs)

- 5Known Issues and Modifications

- 6Revision History

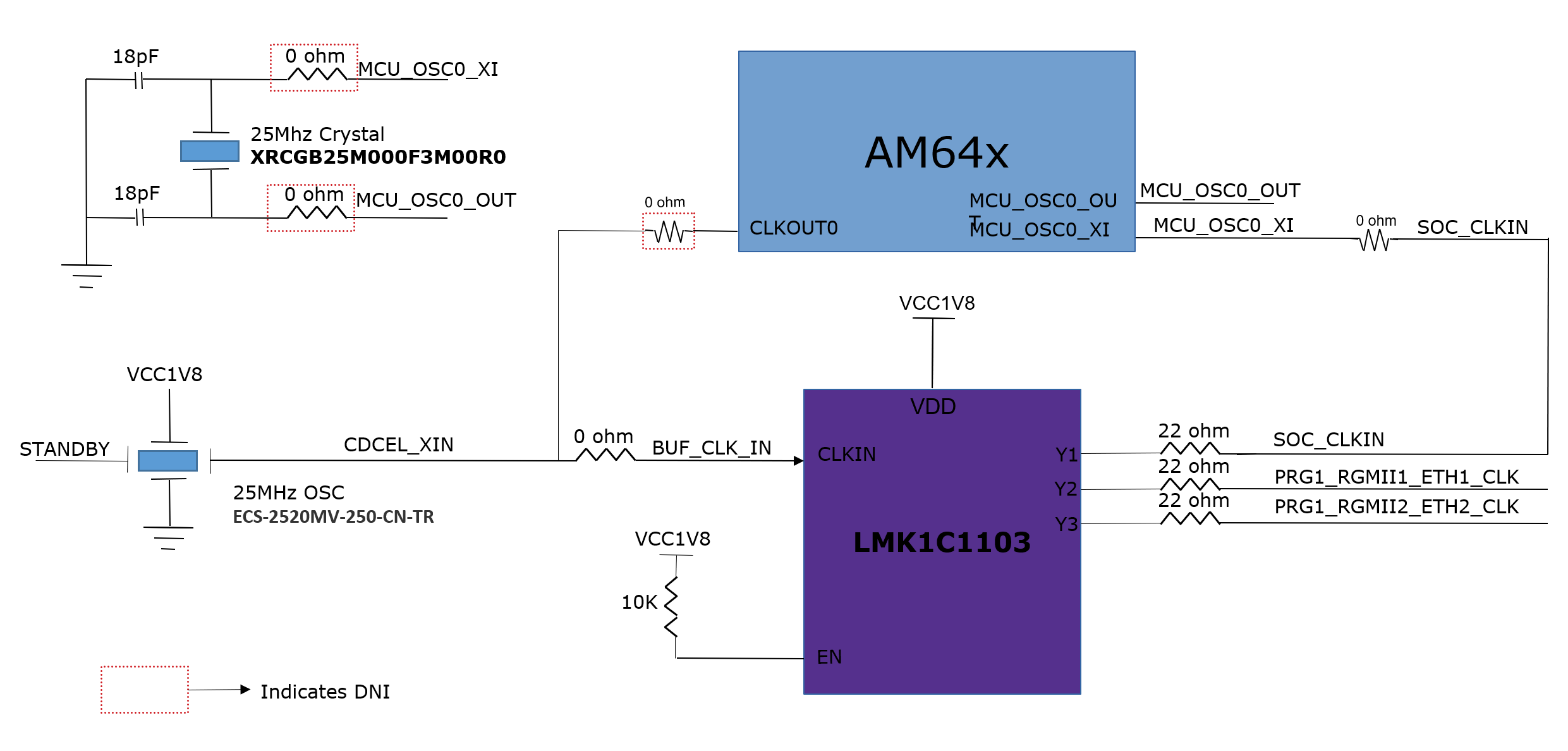

4.1.1 Ethernet PHY Clock

The clock buffer of part number LMK1C1103PWR is used to drive the 25-MHz clock to the Ethernet PHYs. LMK1C1103PWR is a 1:3 LVCMOS clock buffer, which takes a 25-MHz crystal/LVCMOS reference input and provides three 25-MHz LVCMOS clock outputs. The source for the clock buffer will be either the CLKOUT0 pin from the SoC or a 25-MHz oscillator (ECS-2520MV-250-CN-TR); the selection can be made using a set of resistors. By default, the oscillator is used as input to the clock buffer in AM64x SKEVM. Output Y2 and Y3 of the clock buffer LMK1C1103PWR are used as a reference clock input for two Gigabit Ethernet PHYs in SKEVM.

Figure 4-1 AM64x SK EVM Clock

Tree

Figure 4-1 AM64x SK EVM Clock

Tree