ZHCADE7 November 2023 CDCE6214 , CDCE6214-Q1 , CDCE6214Q1TM , LMK00301 , LMK00304 , LMK00306 , LMK00308 , LMK00334 , LMK00334-Q1 , LMK00338 , LMK03318 , LMK03328 , LMK3H0102 , LMK6C , LMK6H , LMKDB1104 , LMKDB1108 , LMKDB1120 , LMKDB1202 , LMKDB1204

5.1.3 带 SSC 的 PNA 测量结果

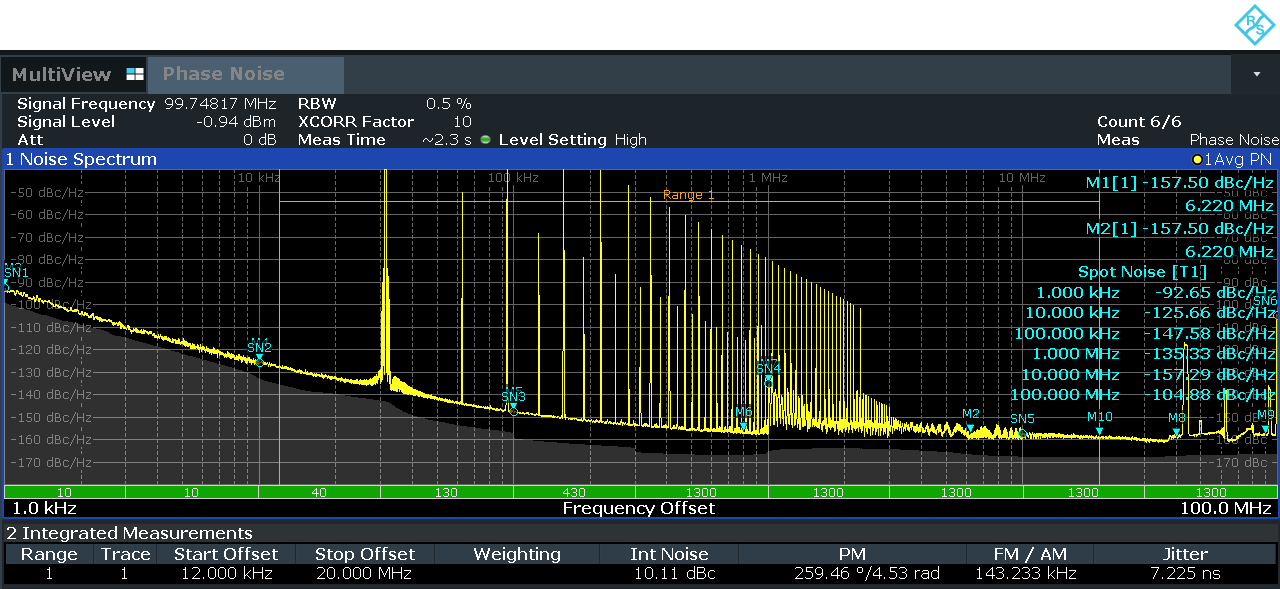

图 5-3 是当启用 SSC 时由 PNA 测量的 LMK3H0102 输出时钟的相位噪声图。SSC 配置为 -0.5% 向下展频调制。由于 SSC 会增加抖动,12kHz 至 20MHz 相位抖动更高,但在应用 PCIe 滤波器时,大部分抖动被滤除。对于 CCS 和 SRIS,最多只能消除 2MHz 的基频和谐波杂散。这样做是为了尽量减少去除与 SSC 无关的杂散。

图 5-3 LMK3H0102 带 SSC 的相位噪声

图 5-3 LMK3H0102 带 SSC 的相位噪声