ZHCA964A September 2019 – July 2020 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

4.2.2 将 VHDL 中的胶合逻辑映射到 CLB

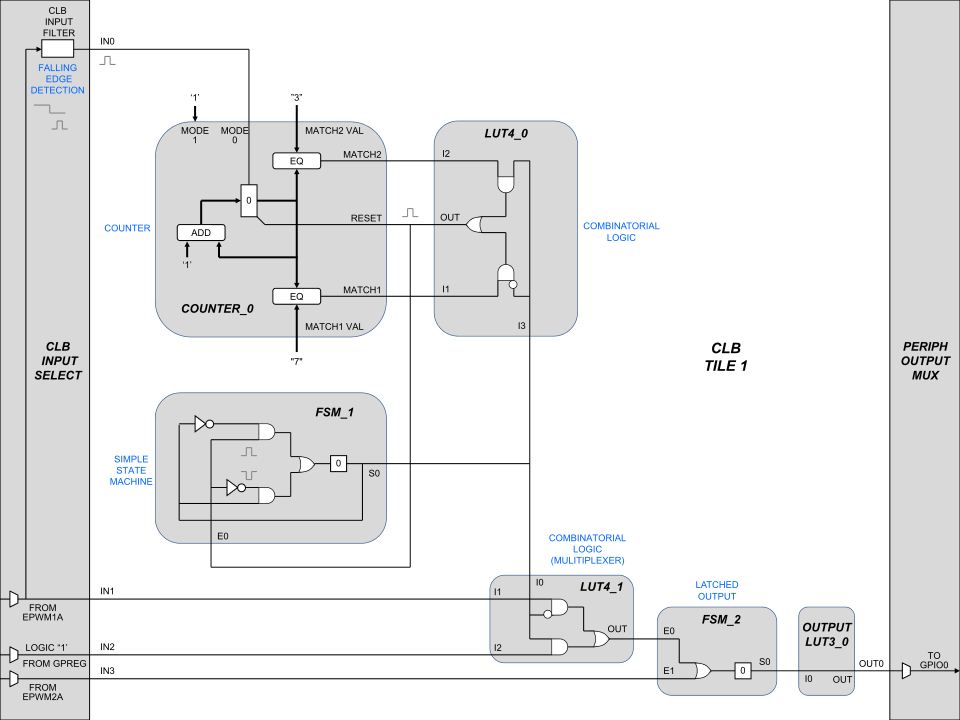

图 2-11 显示形成 CLB 逻辑块的构建块包括三个计数器、三个 LUT4 块(4 输入查找表)、三个 FSM 块(有限状态机)和八个输出 LUT3 块。这些块可通过基于 GUI 的 SysConfig 工具进行编程,该工具根据用户与 GUI 的交互,生成代码来配置相应的逻辑块配置寄存器。将 HDL 代码转换为 CLB 的过程包括四个步骤:

- 使用输入选择功能调用从全局和本地信号总线(或 GPREG 寄存器)中为每个 CLB 逻辑块选择最多八个输入,并使用外设信号多路复用器功能调用指定八个可能的输出中的每一个是否替换所选控制外设内的信号

- 绘制 HDL 代码的功能方框图(如图 4-4 所示)

- 将该方框图细分为最适合映射到特定 CLB 构建块中的更小子部分集合(如图 4-8 所示)

- 使用 SysConfig GUI 分别为每个生成的子部分实现逻辑。

图 4-8 CLB 示例 16 – CLB1 的逻辑分配

图 4-8 CLB 示例 16 – CLB1 的逻辑分配