ZHCA964A September 2019 – July 2020 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

4.3.2 仿真波形

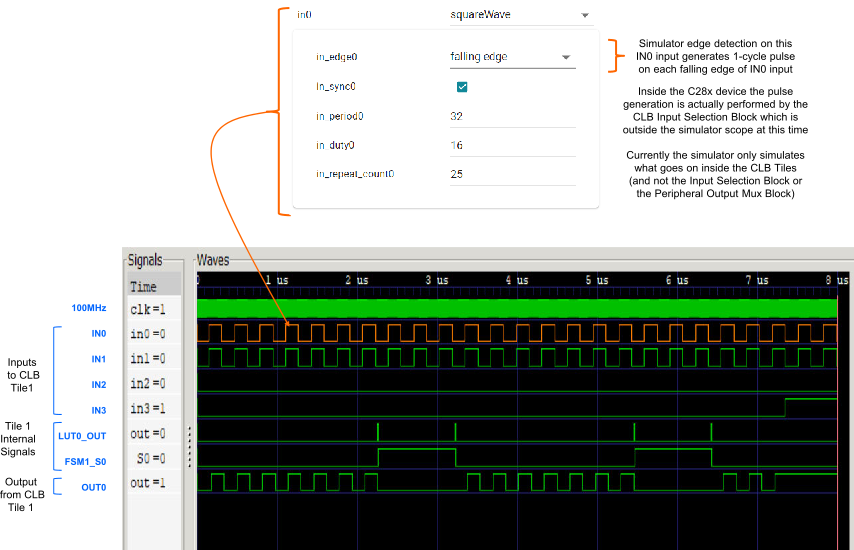

随 C2000Ware 提供的 CLB 工具套件还包括 CLB 仿真器。与逻辑块查看器一样,该工具的当前版本模拟逻辑块,但不模拟输入选择或输出的外设信号多路复用。为了弥补这一点,模拟器可以提供常用输入,如常数、波形和脉冲。这些是使用 SysConfig 工具的 GUI 通过下拉菜单选择(用于配置逻辑块逻辑基元的相同方法)定义的。图 4-10 显示了来自 CLB 仿真器的 CLB 示例 16 的屏幕截图。检查波形,您可以看到四个输入和输出以及一些关键的内部信号。将这些波形与 FPGA 仿真器的波形(图 4-7)进行比较,您可以看到完全匹配,这表明示例 16 的 C2000 版本确实与原始 FPGA 设计相匹配。有关上面使用的功能调用和 SysConfig 代码,请参阅 C2000Ware 示例 16 项目文件。

图 4-10 CLB 示例 16 – CLB 仿真器波形

图 4-10 CLB 示例 16 – CLB 仿真器波形