ZHCA964A September 2019 – July 2020 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

3.2 CLB 示例 17 – 使用 CPU 信号修改外设输入信号

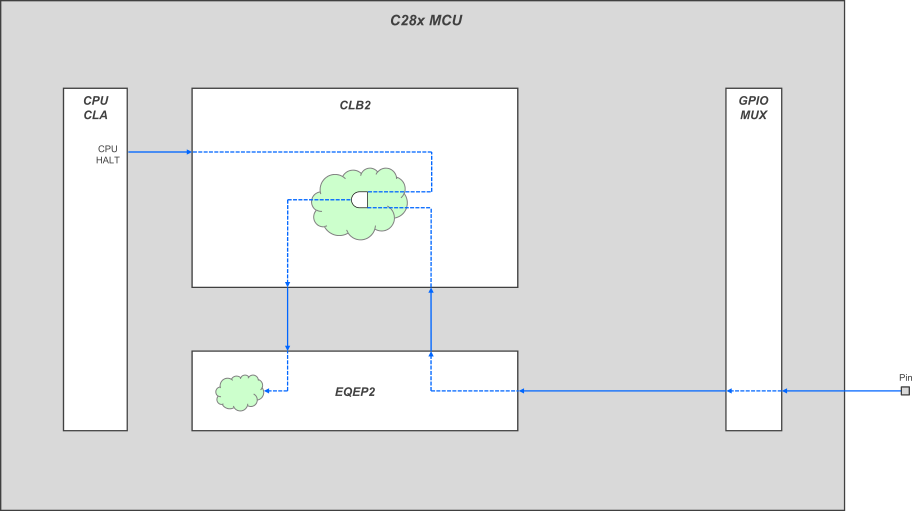

在该示例中,一些自定义逻辑应用于 QEP2 控制外设的输入。图 3-4 显示了该示例的功能原理图。查看信号,可以看到输入由 GPIO 引脚提供,然后输入从该引脚传递到 QEP2。输入信号进入 QEP2 后,立即提取该信号并将其重新路由到 CLB2,该信号在此处与 CPU HALT 信号合并。产生的信号恰好在 QEP 逻辑的第一级之前向回注入到 QEP 中,就好像它是原始输入一样。从这时起,QEP 逻辑进行接管,处理经修改的输入。

图 3-4 CLB 示例 17 – 使用 CPU 信号修改外设输入信号

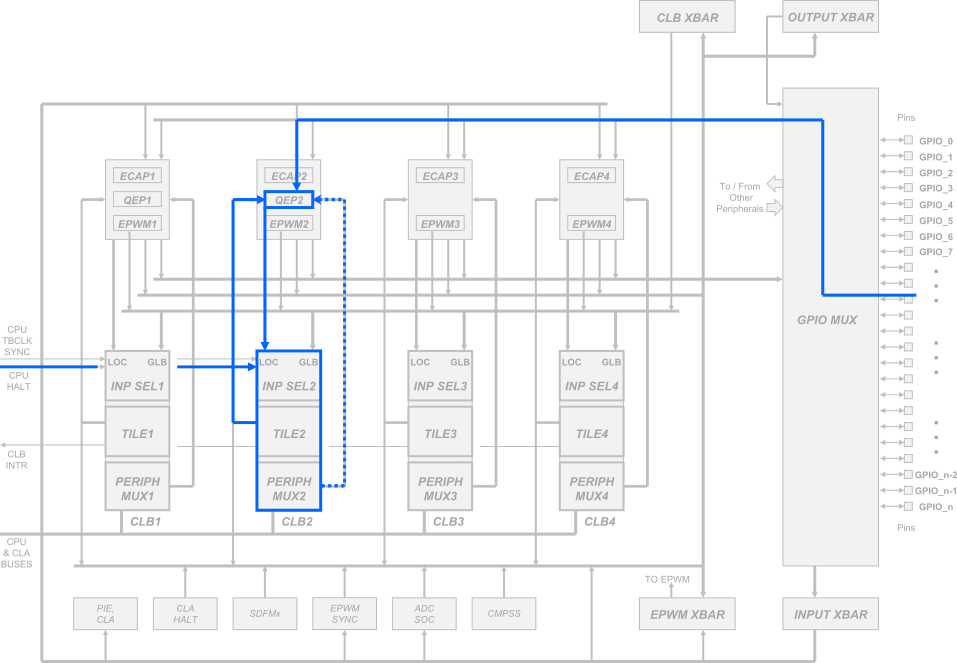

图 3-4 CLB 示例 17 – 使用 CPU 信号修改外设输入信号图 3-5 在器件级视图中显示了相同的示例,以在 I/O 部分的暗灰色背景下突出显示活动块和产生的数据传输。此处同样显示,GPIO 输入在通过 GPIO 多路复用器之后到达 QEP2。它从此处放置在本地 2 信号总线上并转发至 CLB2。CPU HALT 信号也通过同一本地 2 总线进入 CLB2。在这两个信号进入 CLB2 内部之后,经本地 2 总线选择并传递到 CLB 逻辑块 2。它们在此处进行逻辑组合(根据逻辑块 2 配置寄存器)并放置在 CLB2 输出总线上,它们通过该总线反馈到 QEP2 外设。同时,外设信号多路复用器 2 块提供一个多路复用控制信号,该信号指示 QEP2 使用新计算的输入来代替原始输入。然后,以与原始信号相同的方式在 QEP2 内部处理该替换输入。

图 3-5 示例 17 中的信号流 – 器件视图

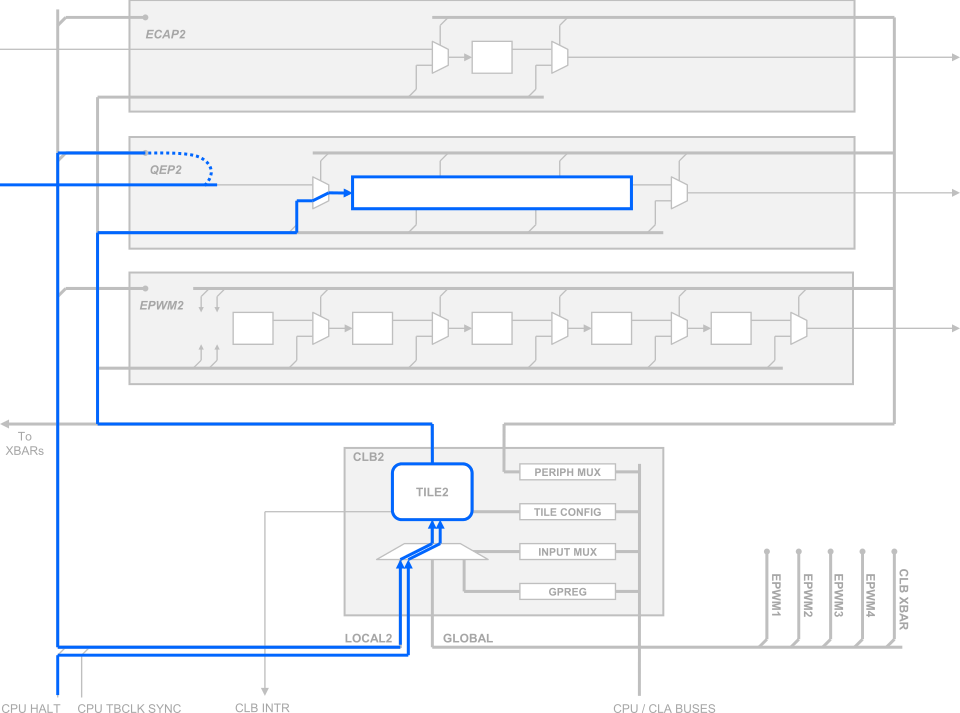

图 3-5 示例 17 中的信号流 – 器件视图图 3-6 在外设级别提供该示例的信号流详细信息,并提供了一定的 CLB2 和 QEP2 外设内部可见性。再次跟踪信号,从进入 QEP2 的原始输入开始立即提取出来,将其放置在本地 2 总线上,该总线还具有 CPU HALT 信号。CLB2 输入多路复用器从此处将这两个信号发送至逻辑块 2,在此处这两个信号组合在一起,并将结果放置在 CLB2 输出总线上,经修改的信号通过该总线代替原始输入信号恰好在第一级之前反馈到 QEP2 中。从此处开始,经修改的输入由 QEP2 进行处理,就好像它是原始输入一样。

图 3-6 示例 16 中的信号流 – CLB2 连接

图 3-6 示例 16 中的信号流 – CLB2 连接