ZHCA964A September 2019 – July 2020 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

2.3.3.1 查找表 (LUT)

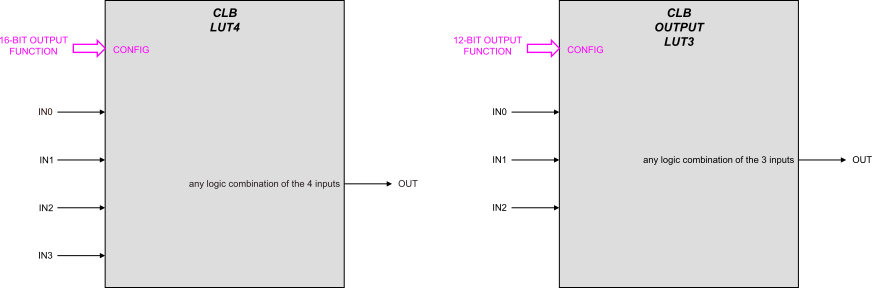

图 2-12 显示了 CLB 逻辑块中使用的两种 LUT:4 输入 LUT4 和 3 输入 LUT3。每个查找表都有一个输出,最后的写操作在HLC侧触发写周期,通过本地接口总线完成数据传输。这些配置寄存器通过 SysConfig 工具生成的代码进行加载。SysConfig 工具还选择逻辑总线的 32 个位中的哪些位用作 LUT 的输入。查找表对输入进行严格的组合逻辑,以生成输出(不存在计时寄存器)。例如,OUT 输出可以是 IN0 输入与 IN1 输入的逻辑或,然后和 IN2 输入进行逻辑与运算。

图 2-12 CLB 查找表

图 2-12 CLB 查找表