ZHCA964A September 2019 – July 2020 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

2.3.3 CLB 逻辑块

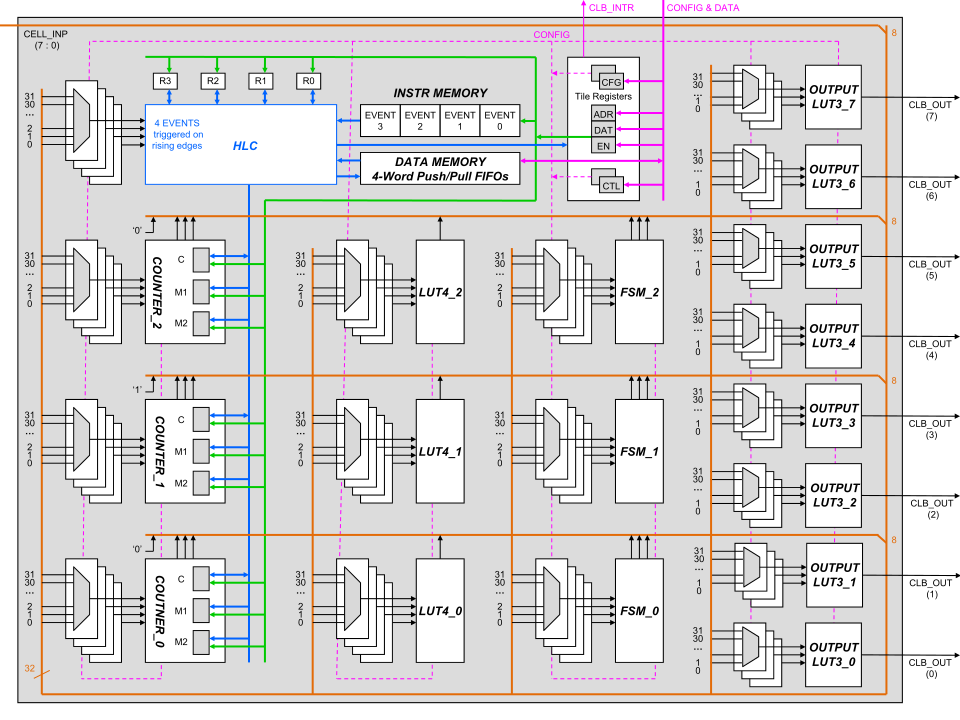

基本级别配置中存在的四个 CLB 模块中的每一个都由一个输入信号选择器、一个 CLB 逻辑块和一个外设信号多路复用器组成。输入信号选择器选择进入 CLB 逻辑块的八个信号,外设信号多路复用器分配 CLB 逻辑块的八个输出。在逻辑块内部,逻辑运算被应用于八个输入(由配置寄存器的内容决定),以生成八个输出信号。这些逻辑运算可以由 HLC 块(高级控制器)、三个计数器、三个 LUT4 块(具有四个输入的查找表)、三个 FSM 块(有限状态机)和八个输出 LUT3 块执行(请参阅图 2-11)。这些逻辑基元中的每一个都由位于 CLB 逻辑块寄存器文件内的相应配置寄存器进行控制,该寄存器文件还包含数据交换寄存器和控制寄存器。C2000 CPU 使用数据交换寄存器来间接访问 HLC 寄存器和计数器寄存器。C2000 CPU 还使用数据交换寄存器来加载 HLC 程序存储器。CPU 使用 SysConfig 工具生成的代码来加载逻辑块配置寄存器。在配置之后,CPU 或 CLA 根据应用代码的指示访问数据交换寄存器和控制寄存器。

图 2-11 显示 CLB 逻辑块的主要特性之一是一条 32 位的逻辑总线(棕色),该总线从所有上述逻辑基元中收集结果位。该总线的最低 8 位来自 CLB 逻辑块的八个输入。随后,全部 32 个位都可用作所有逻辑基元的输入,从而可以轻松共享中间逻辑结果,同时通过八个输入构建八个输出。例如,来自计数器的输出可能在 LUT4 块内与 FSM 块的输出进行“或”运算,以生成进入输出 LUT3 的信号,从而成为 CLB 逻辑块的输出之一。HLC 还可以使用此 32 位内部逻辑总线,在最多四个选定逻辑总线信号从低到高转换时触发最多四个不同的程序。最初通过 SysConfig 工具生成的代码将这四个 HLC 程序预加载到 HLC 指令存储器中,并且每个程序最多可包含 8 条 HLC 指令。

逻辑基元主要用于处理单个信号,而 HLC 可以同时处理信号向量(信号组),例如在四个 HLC 通用寄存器(R0、R1、R2、R3)和三个 CLB 计数器内的选定寄存器(计数、匹配 1、匹配 2)之间交换数据。也可以通过 HLC ADD 和 SUB 指令来修改四个通用寄存器和计数器寄存器。其他指令执行将 HLC 寄存器或计数器寄存器中的数据推入到 4 字 FIFO 中的操作,或执行将 4 字 FIFO 中的输入拉出到 HLC 寄存器或计数器寄存器中的操作。4 字 FIFO 是与主机系统共享的 HLC 数据存储器的一种形式,有助于在 HLC 与 C2000 存储器之间移动数据。图 2-11 中以蓝色突出显示了 HLC 使用的数据移动路径。

在 C2000 侧,可通过存储器映射读取和写入来访问拉/推 FIFO。逻辑块逻辑配置寄存器、控制寄存器和数据交换寄存器,则可以直接访问进行读取和写入。在图 2-11 中,这些 CPU/CLA 传输的路径以品红色突出显示。

CPU 和 CLA 使用数据交换寄存器向 HLC 中无法通过存储器映射读取和写入直接访问的其他资源进行写入(但不读取)。这其中包括 HLC 指令存储器、四个 HLC 通用寄存器和三种类型的计数器寄存器:计数、匹配 1 和匹配 2。CPU 和 CLA 通过数据交换寄存器对 HLC 资源的这些间接访问的工作方式如下:首先,将写入地址加载到 CLB_LOAD_ADDR 寄存器中,接下来将要传输的数据写入到 CLB_LOAD_DATA 寄存器中,然后对 CLB_LOAD_EN 寄存器进行写入。最后的写操作在HLC侧触发写周期,通过本地接口总线完成数据传输。在图 2-11 中,该总线以绿色突出显示。

图 2-11 CLB 逻辑块

图 2-11 CLB 逻辑块以下各节重点介绍构成 CLB 逻辑块的三种逻辑基元(查找表、有限状态机和计数器)的内部细节。