ZHCA964A September 2019 – July 2020 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

4 FPGA 至 CLB 逻辑转换示例 16

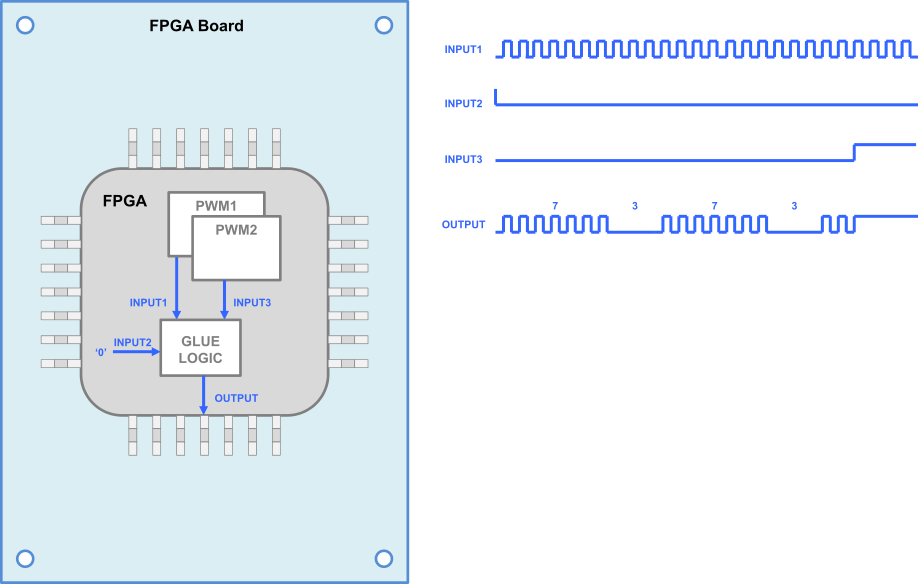

该示例对Topic Link Label3.1中的示例 16 进行了扩展,以演示如何仅使用四个可用的 CLB 逻辑块之一将外部自定义逻辑整合到 C2000 微控制器中。图 4-1 显示了基于 FPGA 的印刷电路板。已使用 VHDL 对 FPGA 进行编程,包括两个 PWM 发生器模块和一个胶合逻辑块,该块将两个 PWM 波形与一个内部信号进行组合以驱动单个输出引脚。仔细观察内部 FPGA 信号,两个 PWM 信号 INPUT1 和 INPUT3 进入胶合逻辑块,在此处它们与静态 INPUT2 信号(逻辑 0)进行组合。在胶合逻辑块内编程的逻辑功能传递 7 个 INPUT1 脉冲,然后输出 INPUT2 信号并维持 3 个 INPUT1脉冲的时间,并重复该模式,直到 INPUT3 变为逻辑 1,此时输出变为高电平(请参阅图 4-1 的波形)。

图 4-1 FPGA 内部具有 PWM 发生器和胶合逻辑的系统板

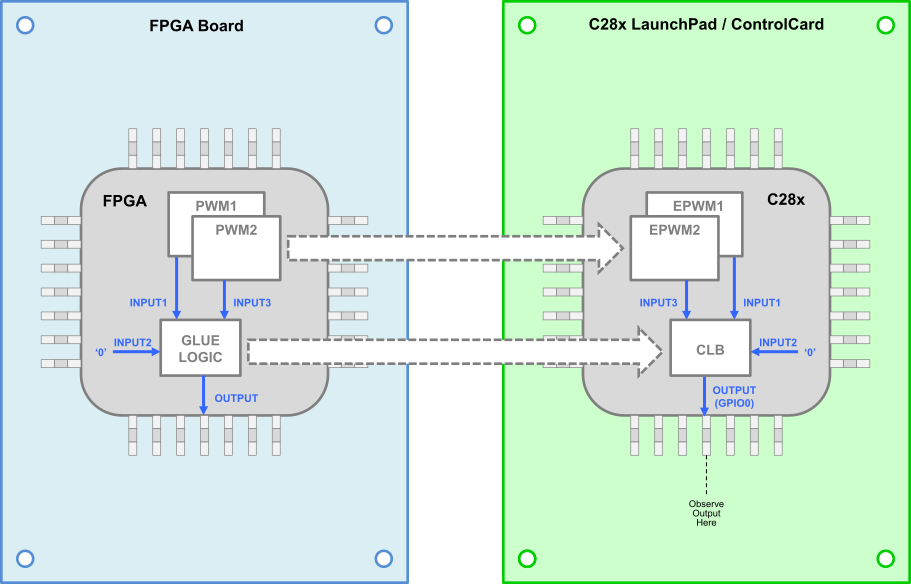

图 4-1 FPGA 内部具有 PWM 发生器和胶合逻辑的系统板图 4-2 形象化地展示了将 FPGA 逻辑吸收到 C2000 器件中的转换过程,其中 EPWM1 和 EPWM2 控制外设提供 PWM 信号,CLB1 提供胶合逻辑。使用 VHDL 对 FPGA 内的胶合逻辑进行编程,而使用功能调用和基于 GUI 的 SysConfig 工具对 CLB1 内的胶合逻辑进行编程(无需了解 VHDL 或 Verilog)。

图 4-2 将 FPGA 中的 PWM 发生器和胶合逻辑映射到 C2000

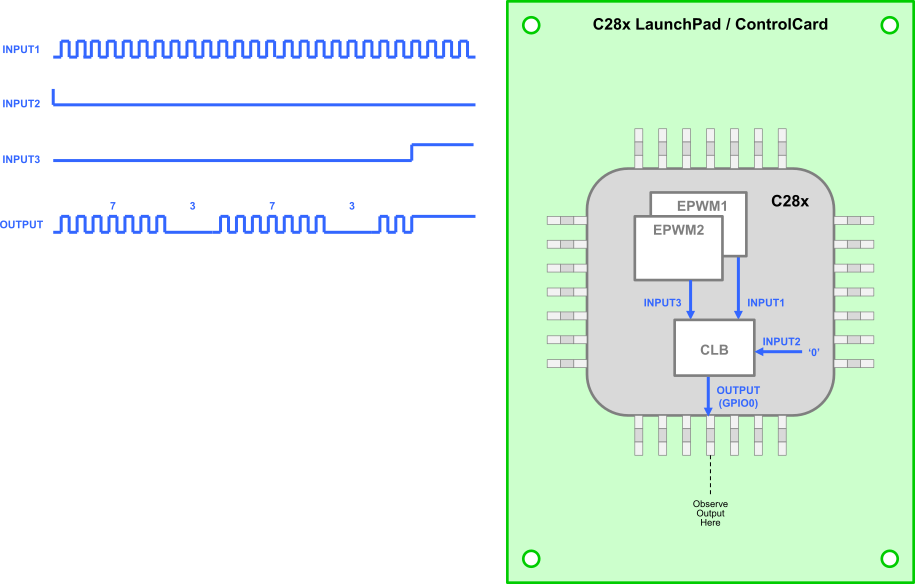

图 4-2 将 FPGA 中的 PWM 发生器和胶合逻辑映射到 C2000图 4-3 基于 C2000 板子产生的波形。比较这些波形,图 4-3 显示它们与 FPGA 板的波形是相同的。本节的剩余部分介绍该示例基于 FPGA 的实现和基于 C2000 的实现的详细信息。这些详细信息包括胶合逻辑的 FPGA 和 C2000 版本的原理图和逻辑波形。此外,还包括 FPGA VHDL 源代码和 C2000 项目文件。

图 4-3 使用 CLB 和两个 EPWM 外设获得的相同结果

图 4-3 使用 CLB 和两个 EPWM 外设获得的相同结果