ZHCA964A September 2019 – July 2020 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

2.1 CLB 如何工作

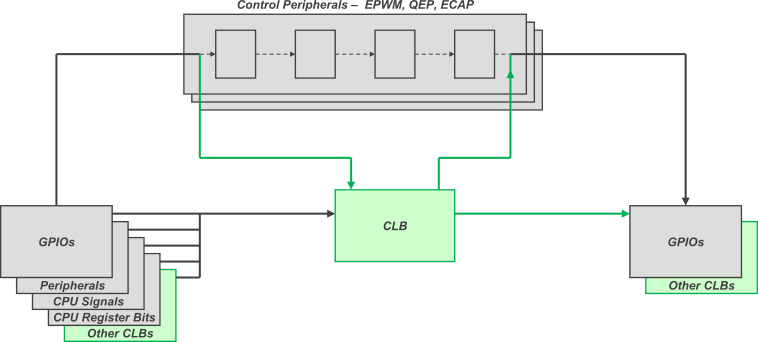

CLB 是可由 CPU 或 CLA 通过配置寄存器进行配置的可编程逻辑基元、输入和输出多路复用器的集合。CLB 模块具有可选的输入和输出信号,这些信号连接选定的控制外设(增强型脉冲宽度调制器 (EPWM)、正交编码器脉冲 (QEP) 和增强型捕捉 (ECAP))内部。根据逻辑基元的配置方式,自定义逻辑作用于来自控制外设内部的输入信号,产生结果送到输出信号,然后把信号向回注入到控制外设内的选定位置。

请注意,进入和离开控制外设的原有输入和输出功能不受 CLB 的影响,只有内部信号能被修改(请参阅图 2-1)。此方法可以修改所选控制外设的操作,或将其完全替换为全新的自定义外设(当在外设边界处分接输入和输出时)。请注意,即使用 CLB 逻辑完全替换了控制外设的内部,外设边界处的输入和输出也不变(相关的通用输入/输出 (GPIO) 功能也是如此)。

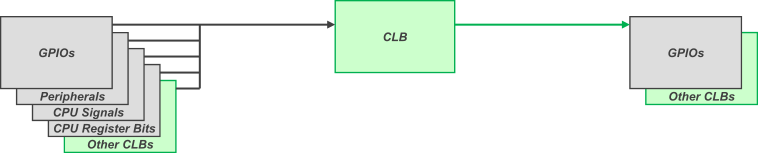

CLB 还可以将输出信号直接驱动到输出 XBAR(交叉开关),这种方式可以在不影响控制外设功能的情况下运行,在输出 XBar 中,可以将这些信号定向为通过选定的 GPIO 引脚输出器件。CLB 的输入不必仅来自控制外设,它们还可以源自其他外设、CPU 信号、CPU 寄存器位和 GPIO。如果 GPIO 是 CLB 的唯一输入,并且 GPIO 是 CLB 的唯一输出,则 CLB 会成为实现以往可能驻留在 FPGA 或 CPLD 中的外部固化逻辑的工具(请参阅图 2-1)。

图 2-2 在控制外设外部运行的 CLB

图 2-2 在控制外设外部运行的 CLB本文档中介绍的所有 CLB 用例本质上都是这两种运行模式的某种组合(请参阅图 2-3)。混合和匹配各种输入和输出的功能使 CLB 成为 C2000 系列的非常灵活强大的补充。以下各节提供了更多系统级信息,以说明 CLB 如何适合 C2000 芯片的其余部分。然后详细考察 CLB 构建块。接下来展示 CLB 的一些最常见示例,包括各种类型的输入和输出用法。。最后,第一个示例将会被更详细的介绍,展示如何将两个 PWM 发生器和相关的胶合逻辑从原来的外部 FPGA 移植进 C2000,以及两种实现方式如何产生相同的结果。

图 2-3 在控制外设内部和外部运行的 CLB

图 2-3 在控制外设内部和外部运行的 CLB