ZHCA964A September 2019 – July 2020 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

4.1.3 测试输入的 VHDL 代码

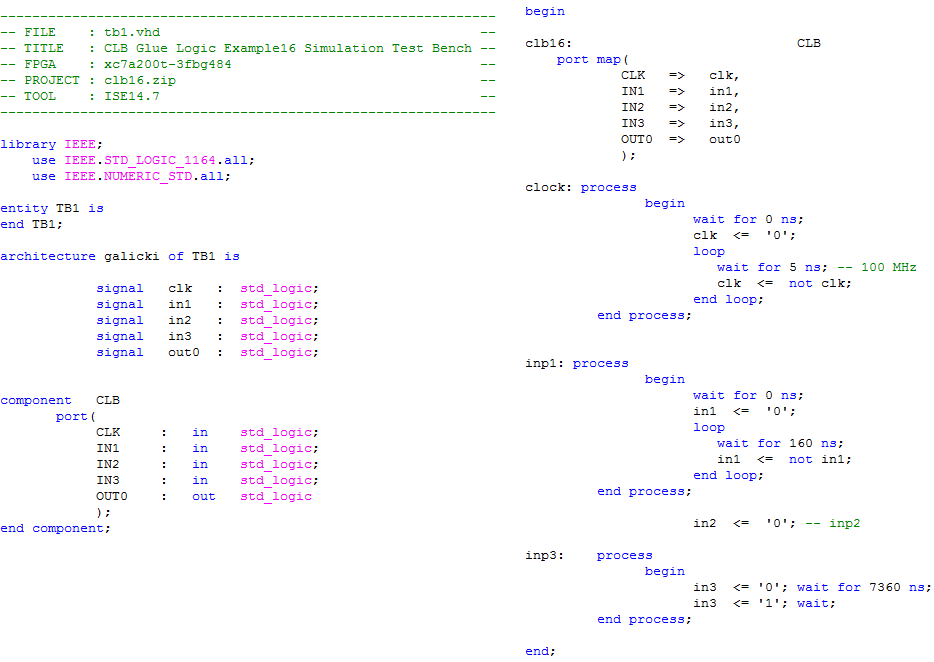

图 4-6 它显示了上述 FPGA 胶合逻辑代码的仿真测试台。该 VHDL 测试台定义了时钟频率和 VHDL 仿真器测试胶合逻辑功能所需的输入状态。查看测试台,可以看到初始语句声明了时钟、三个输入和一个输出。接下来,将其与从测试台实体内部实例化的胶合逻辑实体的相应信号进行匹配。接下来是定义时钟和三个输入的三个过程。时钟频率设置为 100MHz,输入 2 设置为常数逻辑 0。其余两个输入(IN1 和 IN3)模拟 PWM 发生器的输出,其中 IN1 具有高频方波(320ns 周期),IN3 具有低频方波(14.72µs 周期)。仅为输入 3 定义了一个脉冲。

图 4-6 CLB 示例 16 – 胶合逻辑输入的 VHDL 源代码

图 4-6 CLB 示例 16 – 胶合逻辑输入的 VHDL 源代码