ZHCA964A September 2019 – July 2020 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

4.1.4 FPGA 胶合逻辑仿真波形

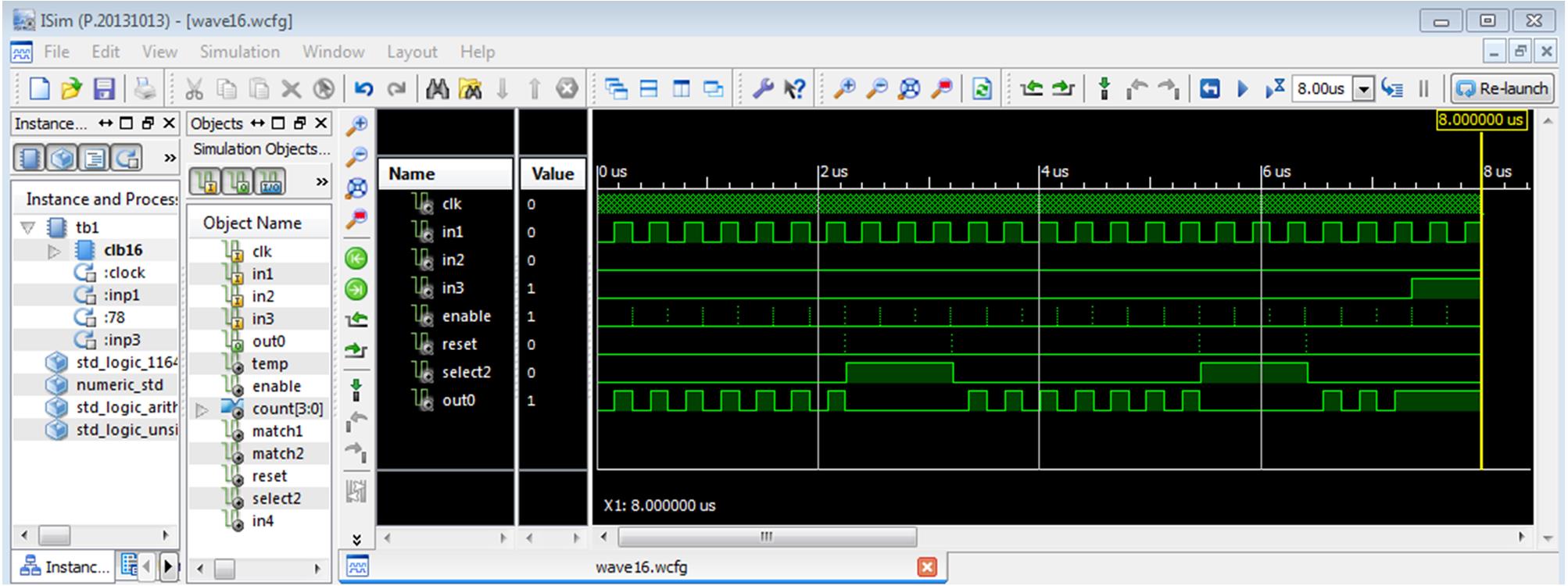

图 4-7 显示了由仿真测试台执行的胶合逻辑功能的仿真结果。除时钟、输出和三个输入之外,波形还显示了关键内部信号:ENABLE、RESET 和 SELECT 2。查看 OUT0 信号,可以发现,很明显,它反映了在上述 VHDL 源代码中编程的预期功能 – 在七个 IN 1 周期中输出 IN1 信号,然后在三个 IN1 周期中变为输出 IN2 信号(逻辑 0),该模式持续发生,直到 IN1 变为逻辑 1,这时 OUT0 被强制变为逻辑 1。

图 4-7 CLB 示例 16 – VHDL 仿真器波形

图 4-7 CLB 示例 16 – VHDL 仿真器波形