ZHCA964A September 2019 – July 2020 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DK-Q1

2.3.1 输入多路复用器

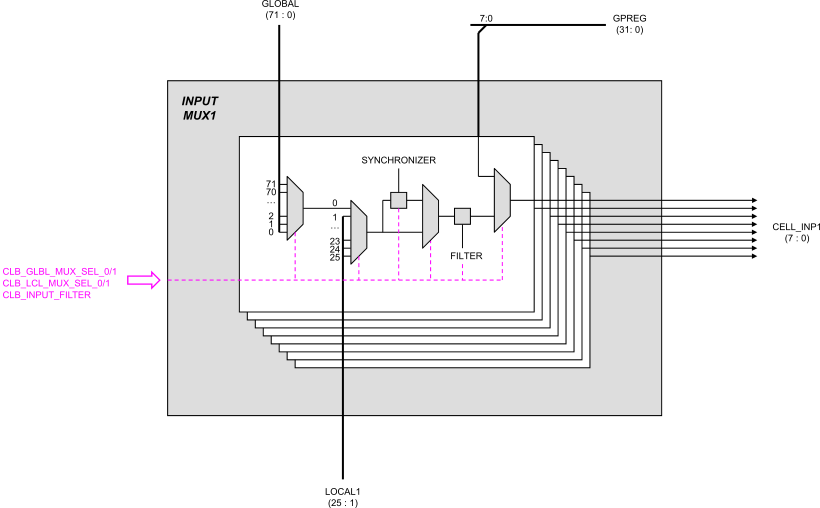

图 2-7 所示为逻辑块 1 的输入多路复用器选择器的详细视图。其他逻辑块的输入多路复用器选择器是相同的,但有几处例外 – 逻辑块 3 和 4 的本地输入信号较少,GPREG 的 32 个位平均分布在四个逻辑块之间(每个逻辑块一个字节,低字节分配给逻辑块 1)。输入多路复用器选择器 1 具有八个相同的部分,每个部分产生一个输出,总共有八个 CLB1 输出信号。在每个部分内部,有一系列多路复用器(共 4 个),从全局多路复用器开始,该多路复用器从 72 个可用输入中选择 1 个位。该位成为下一级的位 0,本地 1 输入信号组提供第 2 级的其余 25 个位。第 2 级的一位输出保持原样地或在通过时钟同步电路之后被传递到下一级。第 3 级的输出通过一个滤波器,在该滤波器中它可能变为上升沿脉冲、下降沿脉冲或保持不变。在最后的第 4 级中,第 3 级的输出可由 GPREG 寄存器中的 8 个位之一替换。同样,输入多路复用器选择器由输入多路复用器配置寄存器通过功能调用进行控制。有关全局和本地信号分配,请参阅特定于器件的技术参考手册 (TRM) 表。

图 2-7 CLB1 的输入选择

图 2-7 CLB1 的输入选择