ZHCU874D February 2021 – August 2021

- 商标

- 1引言

- 2重要使用说明

- 3系统说明

- 4已知问题和修改

- 5参考文献

- 6修订历史记录

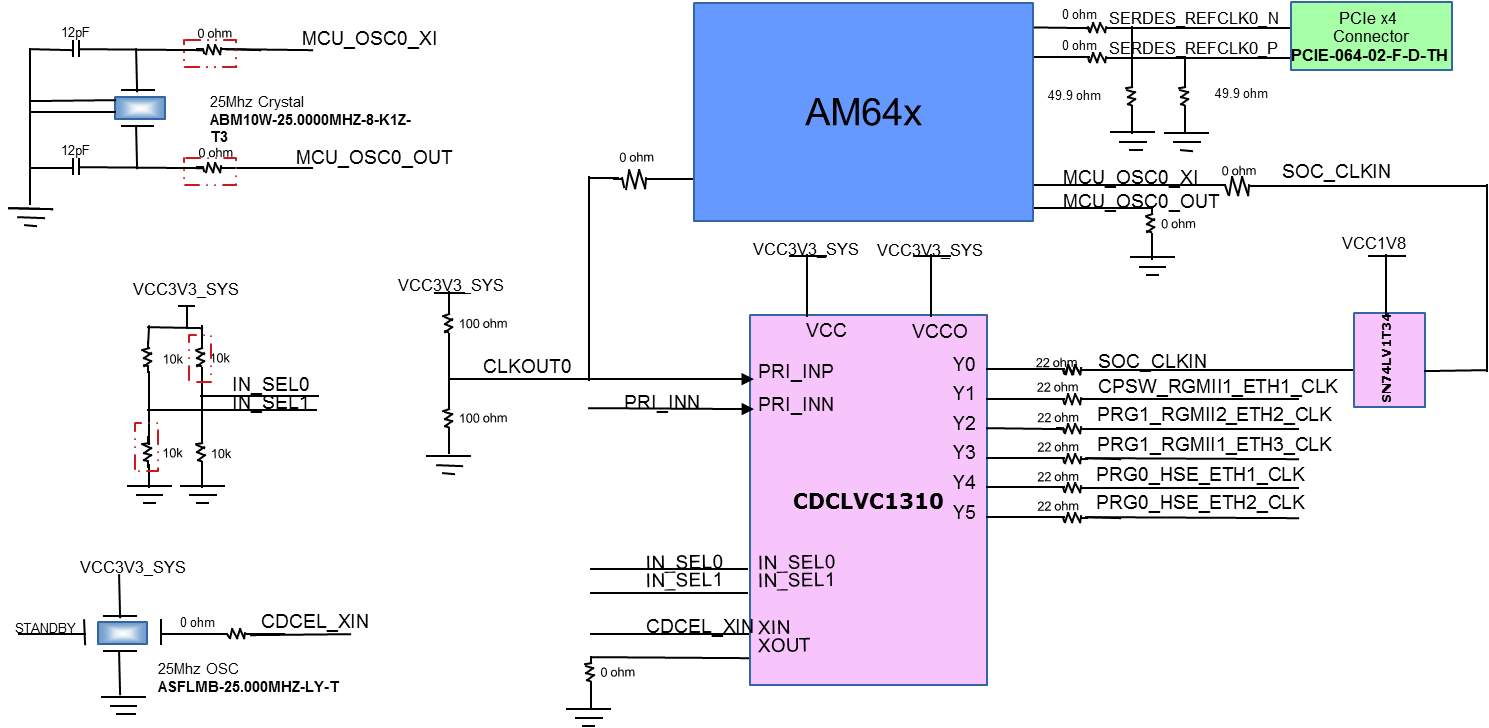

3.4.1.1 以太网 PHY 时钟

器件型号为 CDCLVC1310 的时钟发生器用于驱动以太网 PHY 的 25MHz 时钟。CDCLVC1310 是 1:10 LVCMOS 时钟缓冲器,根据 25MHz 晶体/LVCMOS 参考输入提供十个 25MHz LVCMOS 时针输出。时钟缓冲器的源可以是 SoC 的 CLKOUT0 引脚或一个 25MHz 振荡器 (ASFLMB-25.000MHZ-LY-T),具体可使用一组电阻器进行选择。此选择可通过时钟缓冲器的选择线路来实现。

- IN_SEL0、IN_SEL1 = [00] 用于选择 CLKOUT0。

- IN_SEL0、IN_SEL1 = [01] 用于选择振荡器输入。这是缺省条件。

单端晶体输入的电阻器端接按照特定于器件的数据表提供。

表 3-1 时钟缓冲器的时钟源选择

| IN_SEL1 | IN_SEL0 | 所选时钟 | 安装 | 拆除 |

|---|---|---|---|---|

| 0 | 0 | 来自 SoC 的 EXT_REFCLK | R40、R45 | R248、R253 |

| 1 | 0 | 振荡器输入 | R253、R40 | R45、R248 |

图 3-4 AM64x/AM243x GP EVM 时钟树

图 3-4 AM64x/AM243x GP EVM 时钟树注: 红色框中的电阻器是 DNI。