ZHCU874D February 2021 – August 2021

- 商标

- 1引言

- 2重要使用说明

- 3系统说明

- 4已知问题和修改

- 5参考文献

- 6修订历史记录

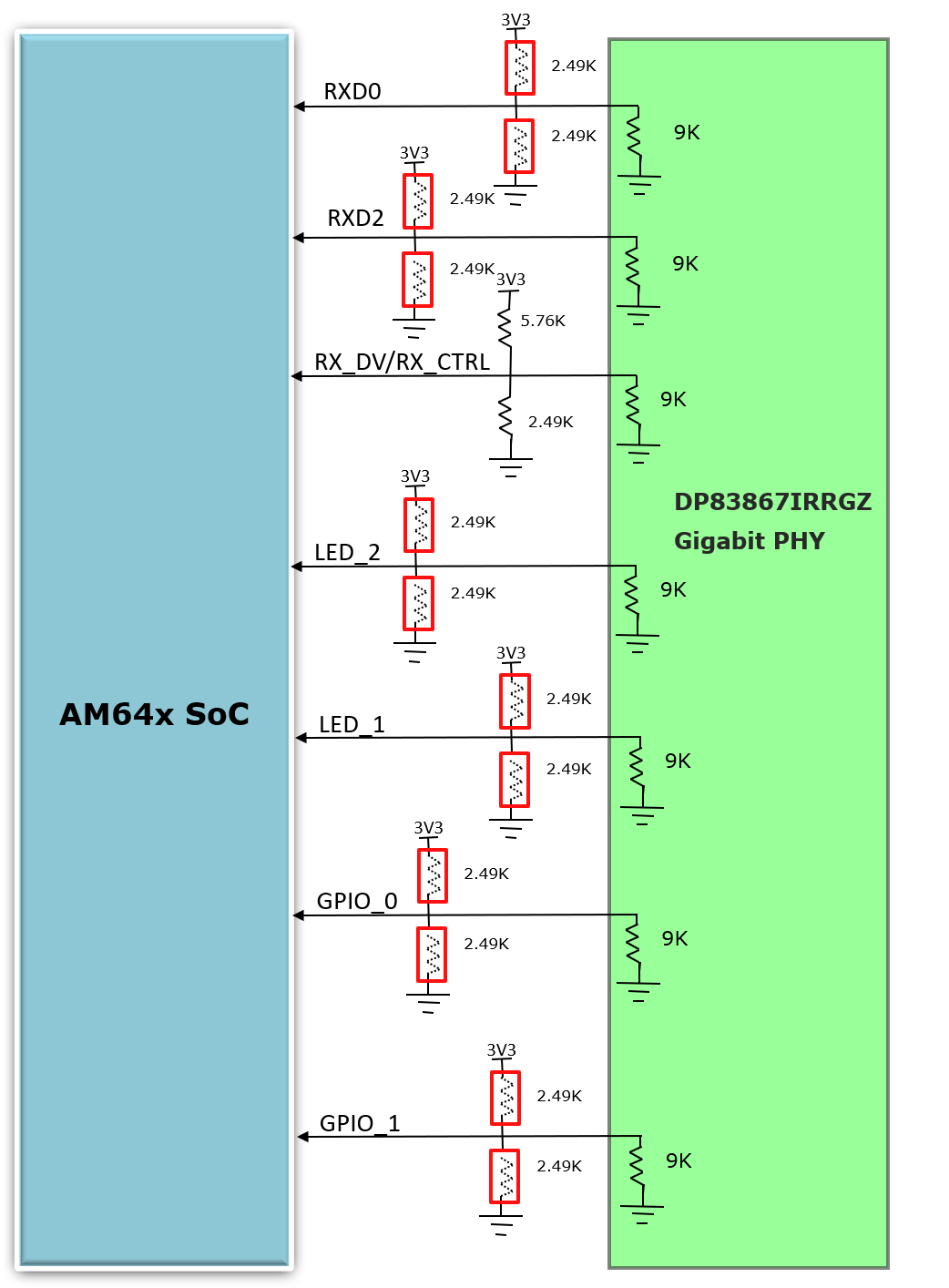

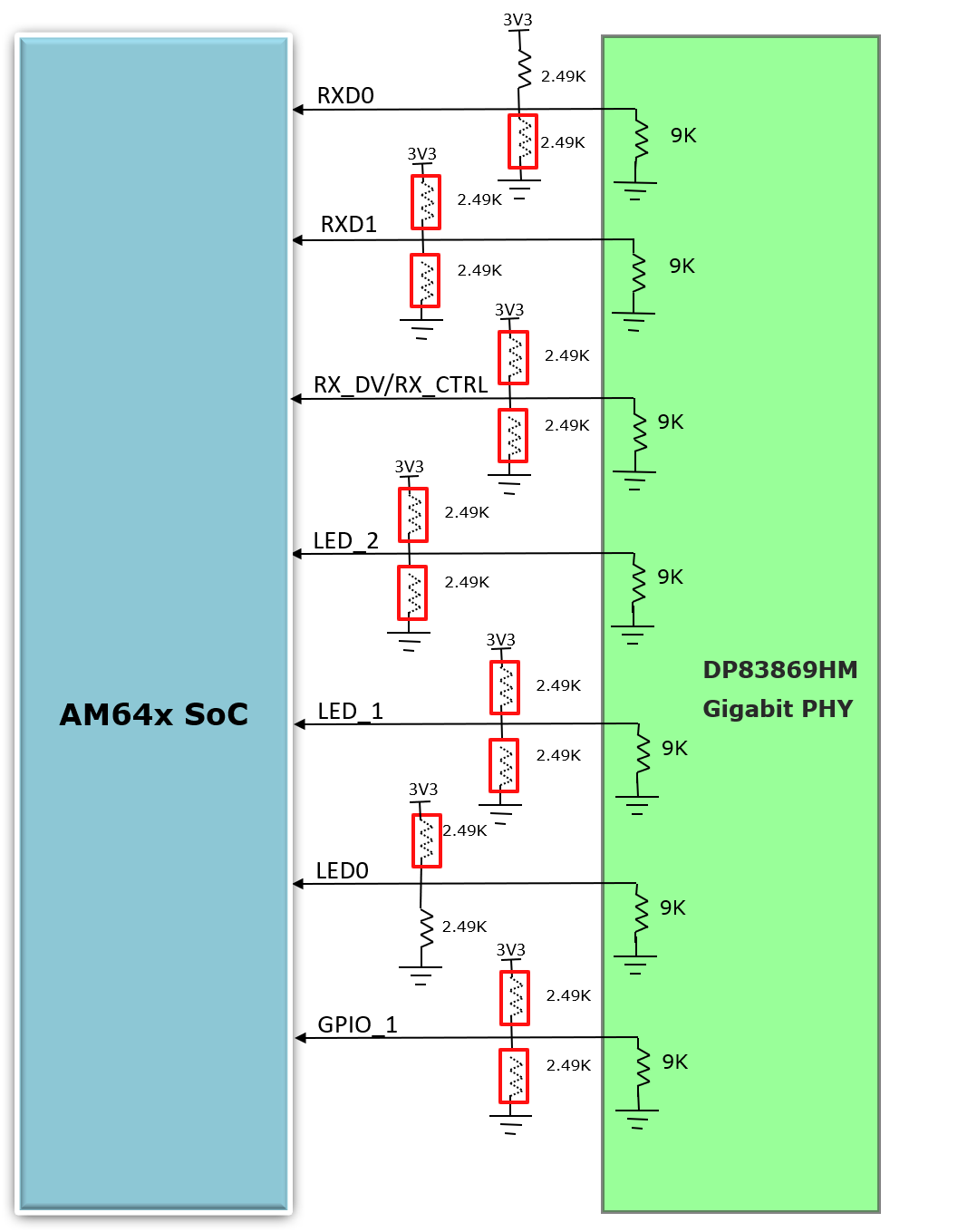

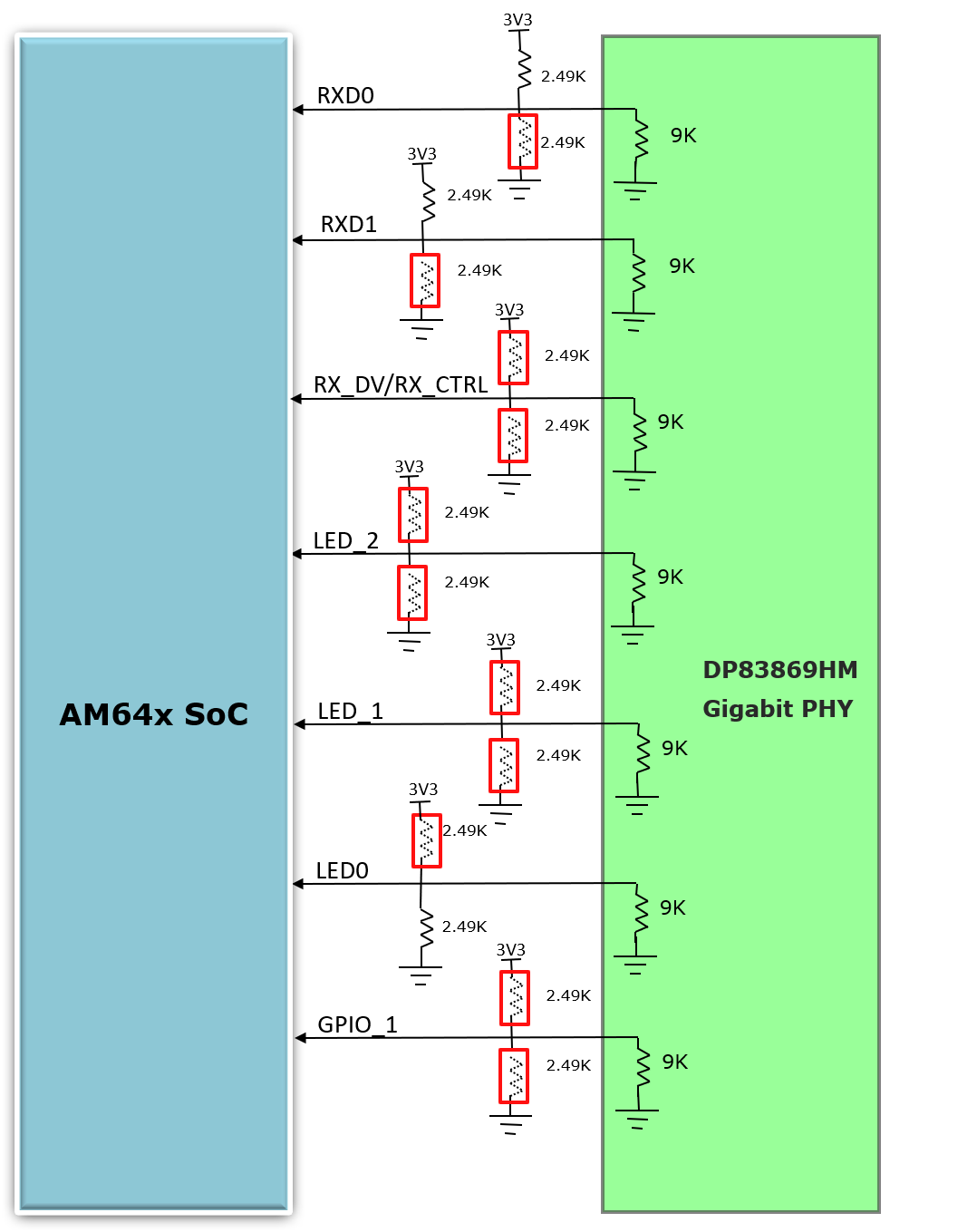

3.4.9.2 DP83869 PHY 默认配置

对于 I/O、RX_D0 和 RX_D1 引脚,DP83869 PHY 采用四级配置,而对于所有其他引脚,则采用两级配置。基于电阻器自举的四级自举引脚可生成四个不同的电压范围。电阻器连接到 RX 数据引脚,它们通常由 PHY 驱动,是 AM64x/AM243x 的输入。每种模式的电压范围如下所示:

模式 0 - 0V 至 0.3069V

模式 1 - 0.4488V 至 0.6072V

模式 2 - 0.7227V 至 0.924V

模式 3 - 1.98V 至 2.9304V

基于电阻器自举的两级自举引脚可生成两个不同的电压范围。这些电阻器连接到 LED 引脚。LED 输出引脚也用作自举引脚,因此必须考虑搭接和 LED 使用所需的外部元件,以避免出现资源争夺问题。具体来说,当 LED 输出直接用于驱动 LED 时,这可能是个问题。每种模式的电压范围如下所示:

模式 0 - 0V 至 0.594V

模式 1 - 1.65V 至 2.904V

DP83869 器件包括内部下拉电阻器。选择外部拉电阻器值时应为 AM64x/AM243x 的引脚提供尽可能接近接地或 3.3V 的电压。自举方式如图 3-21 中所示,而自举电阻值如表 3-20 中所示。

这里使用自举电阻器为 ICSSG1 PHY-1 提供了地址自举,以设置地址 00011 (03h),并为 ICSSG2 PHY 提供了地址自举,以设置地址 01111 (0Fh)。所有自举引脚均提供了上拉和下拉占用空间。

| 自举设置 | 引脚名称 | 自举功能 | PRG0_PRU1、 PRG0_PRU0、 PRG1_PRU1、 PRG1_PRU0 的模式 |

PRG0 和 PRG1 自举功能值 | 说明 |

|---|---|---|---|---|---|

| PHY 地址 | RX_D2 | PHY_AD3 | 1 | 0 | PHY 地址:0000 |

| PHY_AD2 | 1 | 0 | |||

| RX_D0 | PHY_AD1 | 1 | 0 | ||

| PHY_AD0 | 1 | 0 | |||

| 自动协商 | RX_DV/RX_CTRL | 自动协商 | 3 | 0 | 自动协商禁用 = 0 |

| 运行模式 | LED_2 | RGMII 时钟偏差 TX[1] | 1 | 0 | RGMII TX 时钟偏差设为 2ns |

| RGMII 时钟偏差 TX[0] | 1 | 0 | |||

| LED_1 | RGMII 时钟偏差 TX[2] | 1 | 0 | ||

| ANEG_SEL | 1 | 0 | 广播能力 10/100/1000 | ||

| LED_0 | 镜像启用 | 1 | 0 | 镜像启用已禁用 | |

| GPIO_1 | RGMII 时钟偏差 RX[2] | 1 | 0 | RGMII RX 时钟偏差设为 2ns | |

| RGMII 时钟偏差 TX[1] | 1 | 0 | |||

| GPIO_0 | RGMII 时钟偏差 RX[0] | 1 | 0 |

| 自举设置 | 引脚名称 | 自举功能 | PRG1_RGMII2 的模式 (ICSSG1) | PRG1_RGMII2 的自举功能值 (ICSSG1) | PRG1_RGMII1 的模式 (ICSSG2) | PRG1_RGMII1 的自举功能值 (ICSSG2) | 说明 |

|---|---|---|---|---|---|---|---|

| PHY 地址 | RX_D1 | PHY_AD3 | 3 | 1 | 3 | 1 | ICSSG1 PHY 地址:00011 |

| PHY_AD2 | 3 | 1 | 3 | 1 | |||

| RX_D0 | PHY_AD1 | 0 | 0 | 3 | 1 | ICSSG2PHY 地址:01111 | |

| PHY_AD0 | 0 | 0 | 3 | 1 | |||

| 运行模式 | RX_CNTL | 镜像启用 | 0 | 0 | 0 | 0 | 镜像启用已禁用 |

| LED_2 | ANEGSEL_1 | 0 | 0 | 0 | 0 | 自动协商,广播 10/100/1000,Auto-MDI-X | |

| LED_1 | ANEGSEL_0 | 0 | 0 | 0 | 0 | ||

| LED_0 | ANEG_DIS | 0 | 0 | 0 | 0 | ||

| JTAG_TDO/GPIO_1 | OPMODE_0 | 0 | 0 | 0 | 0 | RGMII to Copper (1000BaseT/100Base-TX/10Base-Te) |

PHY 设备集成 MDI 终端电阻器,因此不提供外部端接。

中断:来自 PRG1 域的两个 ICSSG PHY 的中断连接在一起,并连接到 AM64x/AM243x 的 EXTINTN 引脚。另外还提供了将来自 CPSW PHY 的中断连接到 PRG1 ICSSG 中断引脚的选项。

三个可配置的 LED 引脚和一个以太网 PHY 的 GPIO 用于指示链路状态。LED 上可多路复用若干功能,用于不同工作模式。可通过使用 DP83867 器件上的 LEDCR1 寄存器地址 0x0018 和 DP83869 器件上的 LEDS_CFG1 寄存器地址 0x0018 来选择 LED 工作模式。测试配置如下所示。

LED0:默认情况下,此引脚指示链路已建立。其他功能可通过 DP83867 器件中的 LEDCR1[3:0] 寄存器位和 DP83869 器件中的 LEDS_CFG1[3:0] 寄存器位进行配置。LDE0 在 CPSW PHY (DP83867) 中未使用,这也是一个自举引脚,用于设置镜像启用。由于不需要这些功能,因而未提供 LED0 的自举。在 DP83869 ICSSG PHY 中,LED0 连接到 SoC 的 PRG1_PRU1_GPO8 和 PRG1_PRU0_GPO8,用于指示链路状态。此引脚也是自举引脚,具有内部下拉电阻器,用于在 DP83869 器件中设置自动协商禁用选项。默认条件是自动协商,并广播 10/100/1000Mbps 链路。

LED_1:默认情况下,此引脚指示 1000BASE-T 链路已建立。可使用自举电阻器将此设置改为自动协商 10/100Mbps。其他功能可通过 DP83867 器件中的 LEDCR1[7:4] 寄存器位和 DP83869 器件中的 LEDS_CFG1[7:4] 寄存器位进行配置。LED_1 也是自举引脚,具有内部下拉电阻器,用于在 DP83867 器件中设置 RGMII TX 时钟偏差并在 DP83869 器件中选择自动协商模式。由于此引脚在两个器件上均设为有效,如果直接驱动 LED,会导致 LED 照明变暗。因此使用 MOSFET 来驱动 LED,如图 3-23 中所示。

LED_2:默认情况下,此引脚指示接收或发送活动。其他功能可通过 DP83867 器件中的 LEDCR1[11:18] 寄存器位和 DP83869 器件中的 LEDS_CFG1[11:18] 寄存器位进行配置。LED_2 也是自举引脚,具有内部下拉电阻器,用于在 DP83867 器件中设置 RGMII TX 时钟偏差并在 DP83869 器件中选择自动协商模式。默认条件是自动协商,并广播 10/100/1000Mbps 链路,可以使用提供的自举电阻器改变这种条件。如果直接驱动 LED,用于自举设置的上拉电阻器会导致 LED 照明变暗。因此使用 MOSFET 来驱动 LED。

GPIO1:在 DP83867 PHY 中,可通过 GPIO 多路复用器控制寄存器 1 (GPIO_MUX_CTRL1) 将 GPIO 配置为发挥 LED3 的功能,LED 配置可通过编程 LEDCR1 寄存器进行设置。这也是一个自举引脚,用于设置快速链路丢失 (FDP),当前为禁用状态。在 DP83869 PHY 中,可通过 GPIO 多路复用器控制寄存器 (GPIO_MUX_CTRL) 将 GPIO 配置为发挥 LED_GPIO(3) 的功能,LED 配置可通过编程 LEDS_CFG1 寄存器进行设置。这也是一个自举引脚,用于在启动时选择 RGMII to Copper 模式。这可以通过使用 MDC &MDIO 引脚更新 GEN_CFG1 寄存器 – 0x9 来更改为 MII 模式(使用 MII 模式时,应禁用千兆位以太网广播功能,因为 PHY 无法建立速度高达 1000Mbps 的链路)

RJ45 连接器 LED 指示 - CPSW (DP83867):

LED1 和 GPIO1 连接到 RJ45 的双 LED 来指示 10/100MHz 或 1000MHz 链路。橙色 LED 指示速度为 10/100MHz,而绿色 LED 指示速度为 1000MHz

LED2 连接到 RJ45 LED(黄色)以指示发送/接收活动。

RJ45 连接器 LED 指示 - ICSSG (DP83869):

LED1 连接到 RJ45 LED(绿色)以指示速度为 1000MHz

LED2 连接到 RJ45 LED(黄色)以指示发送/接收活动。

图 3-20 AM64x/AM243x 以太网接口 - CPSW 以太网自举设置

图 3-20 AM64x/AM243x 以太网接口 - CPSW 以太网自举设置 图 3-21 AM64x/AM243x 以太网接口 - ICSSG1 以太网自举设置

图 3-21 AM64x/AM243x 以太网接口 - ICSSG1 以太网自举设置 图 3-22 AM64x/AM243x 以太网接口 - ICSSG2 以太网自举设置

图 3-22 AM64x/AM243x 以太网接口 - ICSSG2 以太网自举设置