ZHCABN2 February 2022 UCC14240-Q1

11 使能 (ENA) 和电源正常引脚 (/PG)

UCC14240-Q1 包含初级参考的、 5V TTL 和 3.3V LVTTL 逻辑兼容的、高电平有效使能功能。强制 ENA 为低电平会禁用器件,并将其置于非开关待机模式,此时电流消耗降至 500µA 以下。将 ENA 引脚拉至高电平(高于 2V 阈值)会激活正常的器件功能。ENA 引脚有一个较弱的内部下拉电阻,因此如果该引脚处于开路状态,ENA 引脚将悬空到禁用状态。如果不使用 ENA,则应将其拉高至 2.5V<VENA<5.5V 之间的电压。应注意确保 VENA 不超过 5.5VMAX。

低电平有效、电源正常 (/PG) 引脚为开漏输出,用于指示 UCC14240-Q1 何时不存在故障且输出电压在其调节设定点的 ±10% 范围内。将 /PG 引脚上的上拉电阻 (>1kΩ) 连接到 5V 或 3.3V 逻辑轨。对于不使用 /PG 信号的应用, /PG 可以直接连接到 GNDP。

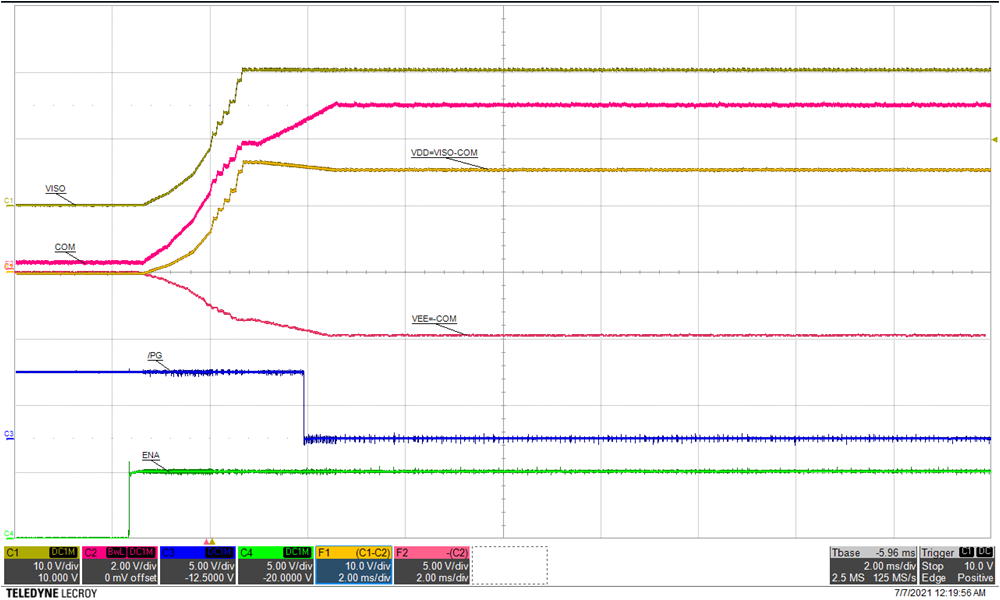

图 11-1 中的启动波形显示了 /PG 相对于 ENA 的预期行为。输入电压(VIN=24V,未显示)已经存在,UCC14240-Q1 由 ENA 变为高电平而激活。ENA 高电平和 /PG 低电平之间的测量时间约为 3.75ms,但可以根据隔离输出电压在设定调节值的 ±10% 范围内所需的时间而变化。相对于 VDD-VEE,COM-VEE 达到调节所需的时间较长,这会导致 VDD-COM 出现轻微的过冲,但这是在 /PG 达到其低电平有效状态之前发生的。这突显了在 /PG 进入有效低电平状态之前请勿切换栅极驱动器的重要性。请注意,此处介绍的波形是从 UCC14240EVM-052 EVM 捕获的。使用 UCC14240EVM-052 用于偏置需要单、正或双、正/负偏置电源的牵引逆变器栅极驱动器 IC 是 EVM 用户指南,其中包含原理图、PCB 详细信息和测量到的性能数据。

图 11-1 启动:VIN=24V,IDD=80mA(顶部:VISO (VDD-VEE),10V/div,中间 1:COM,2V/div,中间 2:VDD=VISO-COM,10V/div,中间 3:VEE=-COM,5V/div,中间 4:/PG,5V/div,底部:ENA,5V/div),时间 = 2ms/div(除非另有说明)。

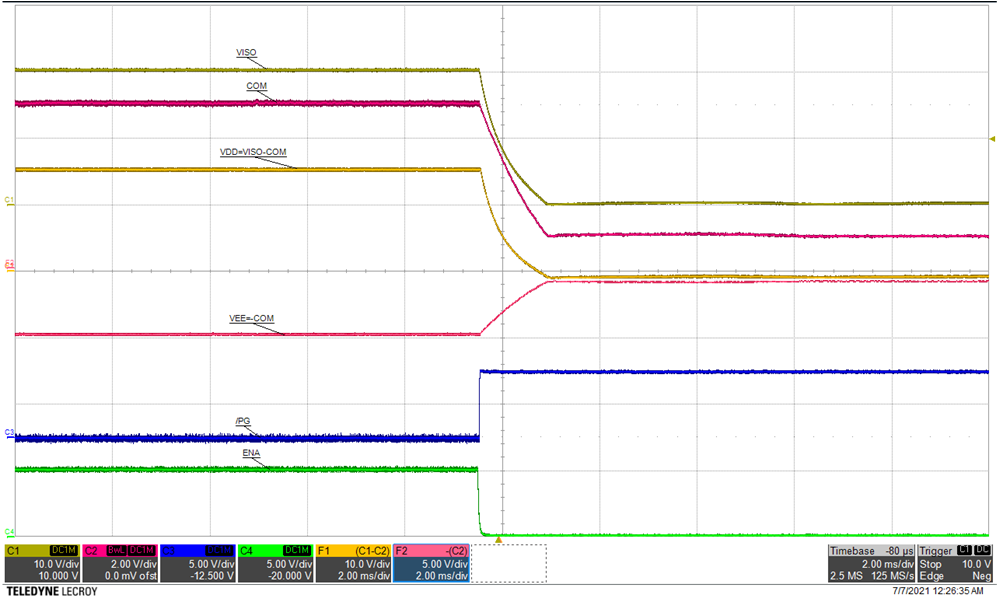

相反,图 11-2 中的关断波形显示,只要 ENA 被拉至为低电平,UCC14240-Q1 输出电压就会以受控方式放电,并且 /PG 在相对于 ENA 几乎没有延迟的情况下切换为高电平。

图 11-2 关断:VIN=24V,IVDD=80mA(顶部:VISO (VDD-VEE),10V/div,中间 1:COM,2V/div,中间 2:VDD=VISO-COM,10V/div,中间 3:VEE=-COM,5V/div,中间 4:/PG,5V/div,底部:ENA,5V/div),时间 = 2ms/div(除非另有说明)。