ZHCABN2 February 2022 UCC14240-Q1

7 电容器选型

UCC14240-Q1 输入和输出高频去耦电容应由一个 2.2µF 陶瓷电容和一个 0.1µF 陶瓷电容并联组成,如图 7-1 和图 7-2 所示。0.1µF 电容器应放置在最靠近 IC 引脚的位置,并且两个电容器的额定电压应至少为所施加电压的 1.5 倍或最小额定电压 35V。UCC14240-Q1 反馈电阻分压器需要 330pF 高频陶瓷旁路电容与下电阻并联。如图 4-1 至图 6-1 的原理图所示,330pF 旁路电容器应在 FBVDD (U1-34) 与 VEEA (U1-35) 和 FBVEE (U1-33) 与 VEEA (U1-35) 之间尽可能相互靠近放置。

图 7-1 导通期间的拉电流

图 7-1 和图 7-2 所示的电路显示了 IGBT 导通期间的拉电流和关断期间的灌电流。UCC14240-Q1 为 UCC21732-Q1、±10A 隔离式 SiC/IGBT 栅极驱动器提供正负双偏置电压,驱动一个 总栅极电荷为 1.75µC 的IGBT。图表已经过简化以突出 CVDD 和 CVEE 的功能和选型。CVDD 和 CVEE 是与栅极驱动器相关的电容器,但在使用图 5-1 所示的双路 VDD/VEE 输出电压配置时,也会对 UCC14240-Q1 的性能产生深远影响。

CVDD 是 UCC21732-Q1 VDD 大容量电容器在导通期间为 Q1 提供所需的电荷,应放在尽可能靠近栅极驱动器引脚的位置。由 ISRC 从 CVDD 消耗的总电荷必须在每个开关周期由 IDD 补充。以 IGBT 的开关频率消耗和补充 CVDD 中的电荷,会导致 CVDD 上产生不可避免的纹波电压变化。由于总电荷由 CVDD 和 CVEE 的串联组合提供,假设所需的纹波电压限制为 ΔV=500mVPP,则所需的总电容可由Equation10 确定,其中,电容越高,纹波电压越低。

根据 1.75µC 的 IGBT 栅极电荷所需的等效电容 CG 与Equation11 所需的电容相比要小得多。因此,3.5µF>>87.5nF 验证了维持所需纹波电压所需的电容始终高于 SiC/IGBT 所需的 CG。

在导通期间,IGBT 需要从 CVDD 获取一定量的电力,从而与 UCC14240-Q1 传输的电量相等,如Equation12 所示:

在关断期间,存储在 IGBT 栅极电容中的总电荷通过应用与 IGBT 并联的 CVEE (-5V))而被移除。关断期间,从 CVEE 移除的电荷也必须通过 UCC14240-Q1 补充和提供,并由Equation13 计算得出:

由于开关事件,所需的总动态功率是Equation12 和Equation13 的和:

根据 UCC21732-Q1 数据表,使用 5.9mA 的最大 IQ_VDD 来计算静态电流消耗所需的功率:

根据Equation16,将 PSW 与 PIQ 结合即可得所需的总偏置功率如下:

应使用Equation16 的结果来验证所需的功率小于在高达 105°C 环境温度下的最大 UCC14240-Q1 功率 1.5W。在本示例中,结果为 847.5mW<1.5W。

图 7-2 关断时灌电流

Equation10 可以改写为:

CVDD、CVEE 电容分压器的第二项功能是根据负 VEE 电压相对于正 VDD 电压的期望值来平衡中点 COM 电压。由 CVDD 和 CVEE 组成的分压器会得到:

将Equation17 设为与Equation18 相等并求解 CVDD 会得到:

CVDD=4.67µF,然后可使用该电容求解 Equation20中的 CVEE。

值得重申的是,CVDD 和 CVEE 是 VDD 和 VEE 相对于 COM 所需的最小总电容值。添加适当的降额并选择大于所示最小计算结果的标准元件值,然后进行调整以保持正确的 CVDD 与 CVEE 比值(根据Equation20)。一旦选择了值,现在可以将 CVDD 和 CVEE 代入Equation10 和Equation19,以验证所选电容器值是否满足所需的 ΔV、纹波电压以及设置由Equation19 确定的正确中点电压。可能有必要使用不同电容器元件值的并联组合来获得所需的比率。

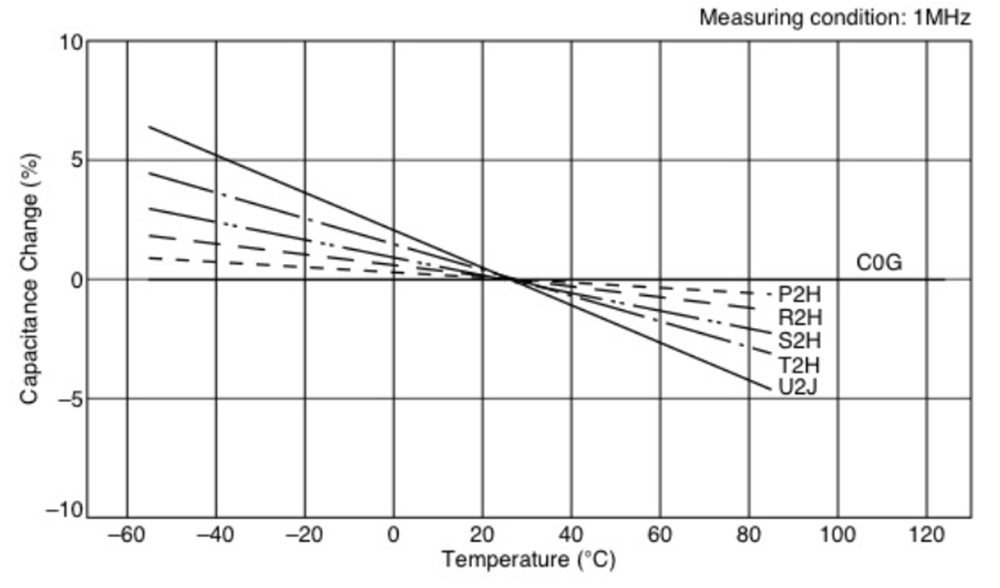

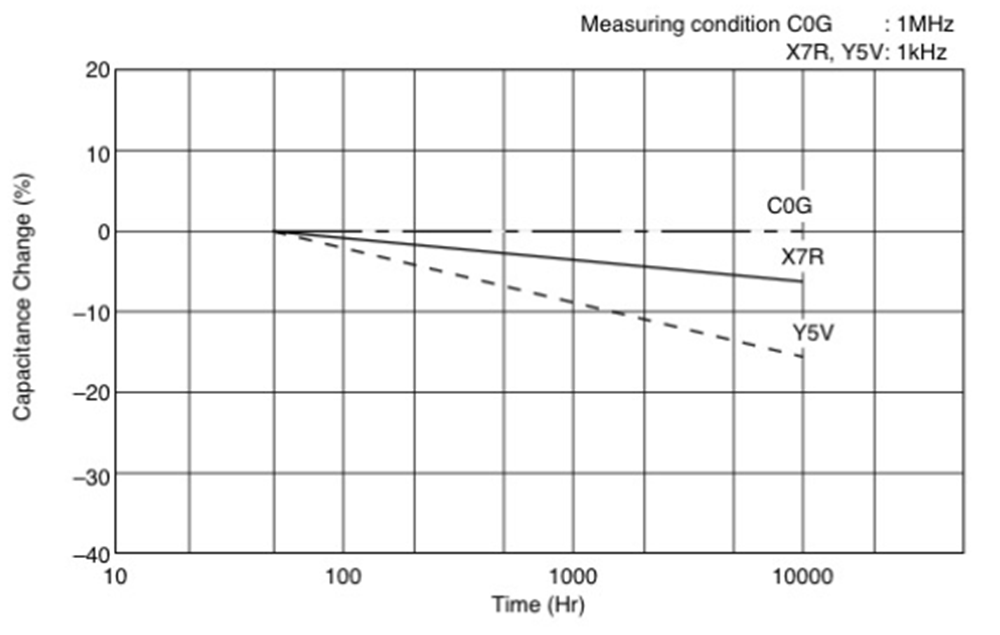

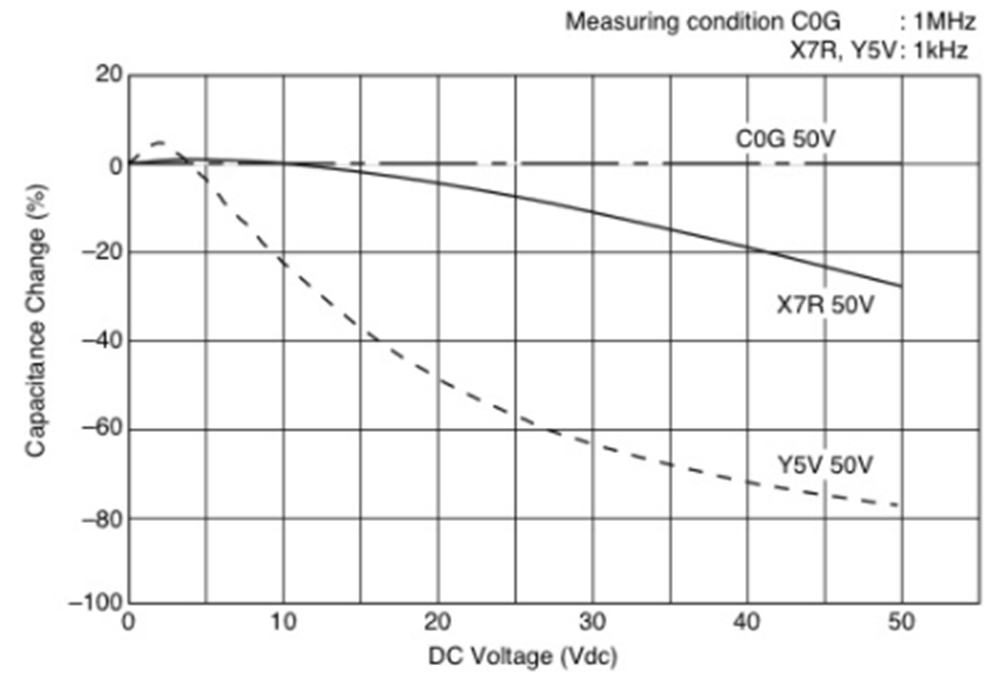

降低纹波电压、VCE 下降电压或提高动态栅极驱动性能是增大 CVDD 电容值的几个可能原因。为了保持正确的 CVDD 与 CVEE 电容分压比(本例中为 3:1),重要的是调整 CVEE 电容值以匹配引入到 CVDD 电容值的任何变化。CVDD 电容器的额定电压应为 35V 或更高,但 CVEE 电容器的额定电压可以较低,适当降低额定电压以处理大约 1.5x 的 VEE。CVDD 和 CVEE 应为具有 X7R 或更优电介质的陶瓷表面贴装电容器,并符合 AEC-Q200 标准,可满足应用的预期温度要求。如果想要达到所需的最小电容,应特别注意所施加的直流电压与电容器额定工作电压、温度、容差和电介质类型的关系,如图 7-3 至图 7-5 所示。要实现最佳的偏置和栅极驱动器性能,需要在所有电气和环境运行条件下满足最小计算电容。

图 7-3 陶瓷电容器温度特征

图 7-4 陶瓷电容器老化特征

图 7-5 陶瓷电容器施加的直流电压特征