ZHCAAN8E september 2022 – may 2023 AM68 , AM68A , AM69 , AM69A , DRA829J , DRA829J-Q1 , DRA829V , DRA829V-Q1 , TDA4VM , TDA4VM-Q1

3.6.3 模型验证

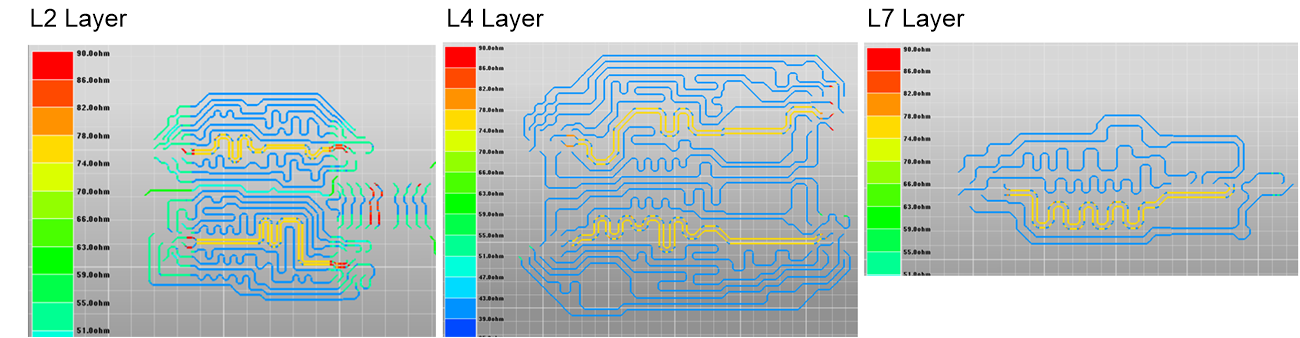

在仿真之前,建议对模型进行验证。介绍的一种验证方法是阻抗图(或阻抗扫描)。提供了 10 层设计的阻抗扫描。

图 3-10 LPDDR4 布线阻抗扫描示例

图 3-10 LPDDR4 布线阻抗扫描示例表 3-8 LPDDR4 示例布线阻抗数据汇总

| 层 | DDR 总线 | DQ SE 阻抗 (Ω) | DQS/CLK 差分阻抗 (Ω) |

|---|---|---|---|

| L2 | B1 和 B3 | 40.9 | 77.7 |

| L2 | CA | 51.7 | 101.4 |

| L4 | B0 和 B2 | 41.1 | 77.7 |

| L7 | CA | 41.1 | 77.7 |

对于 CK 和 CA 信号,目标是使分支段阻抗等于馈送布线阻抗的两倍。请注意,PCB 限制可实现的阻抗是很正常的。仿真将向您展示折衷是否可以接受。

表 3-9 LPDDR4 示例布线阻抗 CA 汇总

| 板 | CA 馈送阻抗 (Ω) | CA 分支阻抗 (Ω) | CA 分支目标 (Ω) | 阻抗不匹配 (Ω) |

|---|---|---|---|---|

| 初始设计 | 49.1 | 59.6 | 98 (49x2) | 38.6 |

| 最终设计 | 41.1 | 51.7 | 82 (41x2) | 30.5 |

仿真结果显示了通过将阻抗与其目标更接近地匹配而实现的改进。

表 3-10 改进布线阻抗后的 LPDDR4 示例仿真结果

| 板 | 总眼图宽度裕度 (ps) | 总眼图高度裕度 (ps) | 最小回铃裕度 H (mV) | 最小回铃裕度 L (mV) |

|---|---|---|---|---|

| 初始设计 | 58.00 | 14.00 | 69.59 | 18.18 |

| 最终设计 | 124.68 | 48.08 | 89.43 | 25.49 |