ZHCU877B May 2021 – October 2023

- 1

- 摘要

- 商标

- 1关键特性

- 2EVM 版本和组件型号

- 3重要使用说明

- 4系统说明

- 5已知问题

- 6法规遵从性

- 7修订历史记录

4.4.1.1 以太网 PHY 时钟

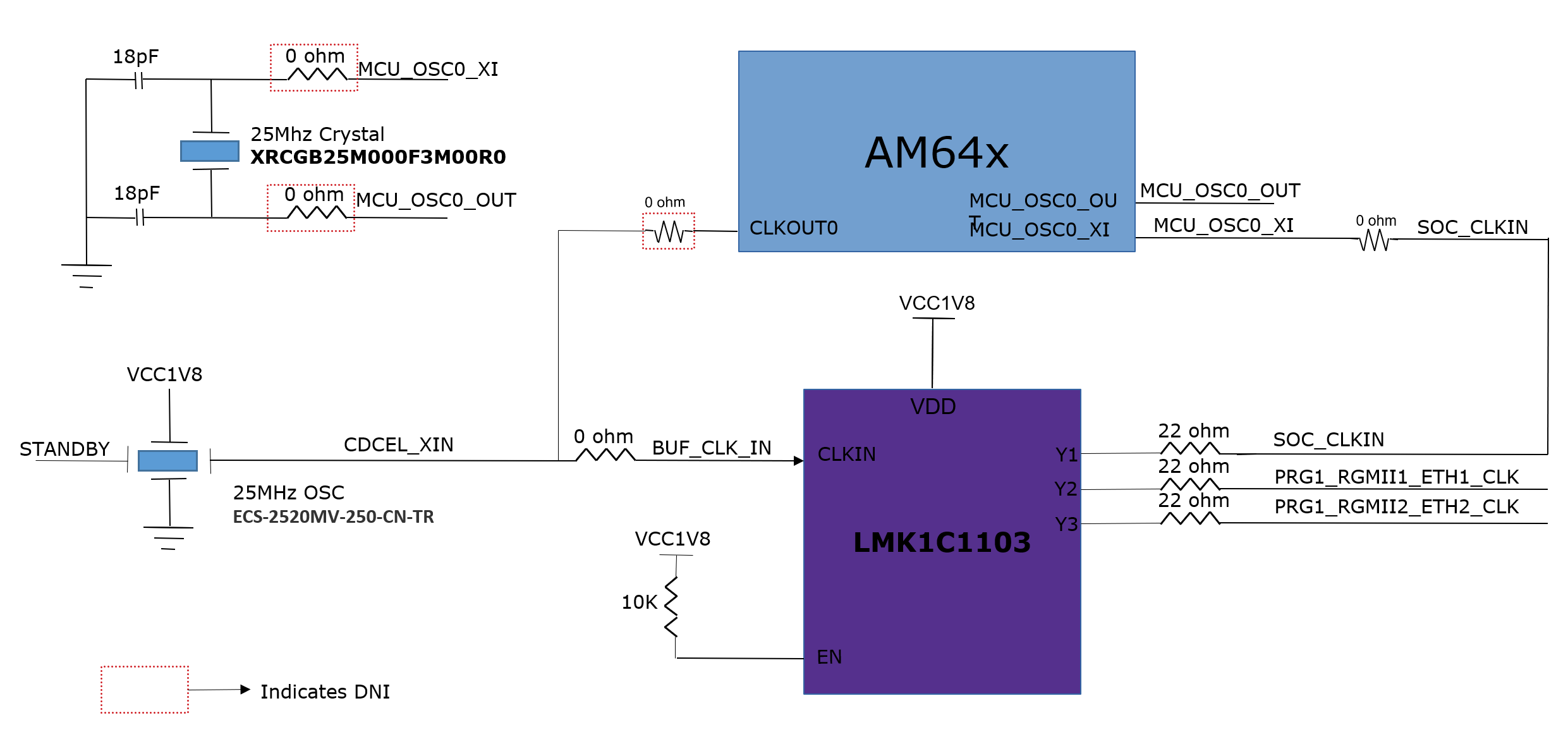

器件型号为 LMK1C1103PWR 的时钟缓冲器用于驱动以太网 PHY 的 25 MHz 时钟。LMK1C1103PWR 是 1:3 LVCMOS 时钟缓冲器,根据 25 MHz 晶振/LVCMOS 参考输入提供四个 25 MHz LVCMOS 时针输出。时钟缓冲器的源是 SoC 的 CLKOUT0 引脚或一个 25MHz 振荡器 (ECS-2520MV-250-CN-TR)。可以使用一组电阻进行选择。默认情况下,振荡器用作 SK-AM64B EVM 中时钟缓冲器的输入。时钟缓冲器 LMK1C1103PWR 的输出 Y2 和 Y3 用作 SKEVM 中两个千兆位以太网 PHY 的参考时钟输入。

图 4-6 AM64x SK EVM 时钟树

图 4-6 AM64x SK EVM 时钟树注: 红色框中的电阻器是 DNI。