ZHCU877B May 2021 – October 2023

- 1

- 摘要

- 商标

- 1关键特性

- 2EVM 版本和组件型号

- 3重要使用说明

- 4系统说明

- 5已知问题

- 6法规遵从性

- 7修订历史记录

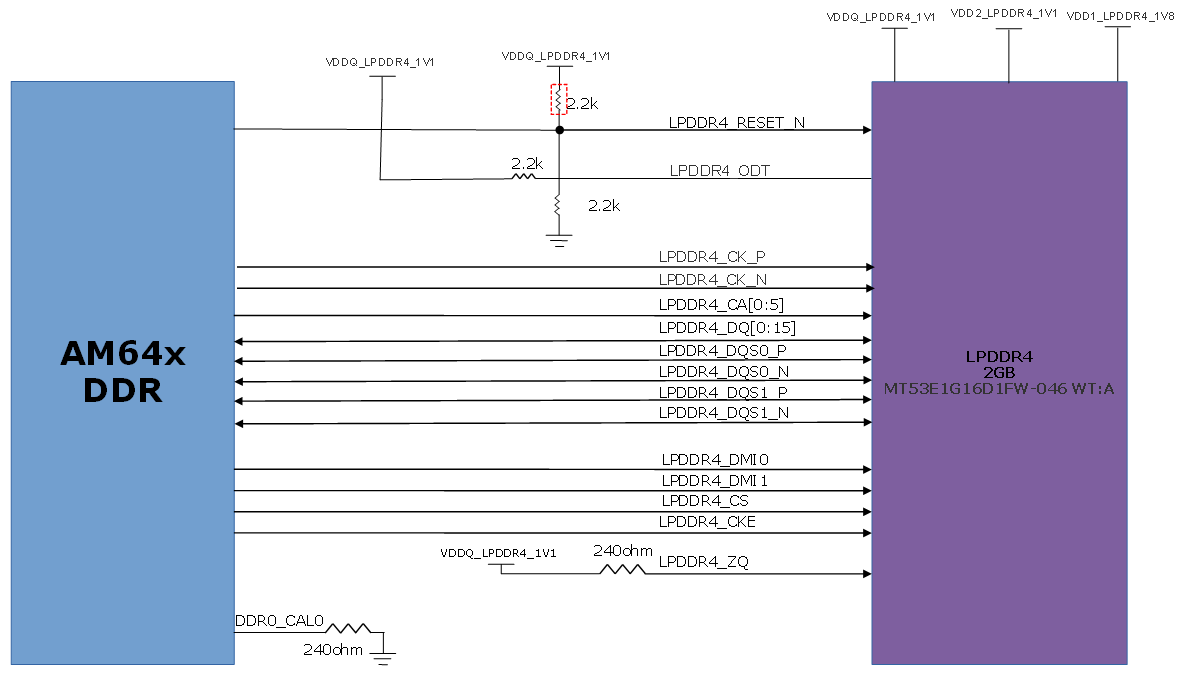

4.4.8.1 LPDDR4 接口

SK EVM 具有 2GB、16 位宽 LPDDR4 存储器,运行数据速率为每引脚 4226Mbps。使用 Micron 的 MT53E1G16D1FW-046 WT: A。LPDDR 存储器采用板载安装形式(单芯片),需要 1.1V,降低了功率需求。LPDDR4 器件需要 1.1V 的 I/O 功率和内核 2 功率,以及 1.8V 的 DRAM 激活电源(内核 1)。

LPDDR4 复位是由 SOC 控制的低电平有效信号,将该信号上拉可设置默认有效状态,也提供了下拉空间。一个 240Ω 电阻从 ZQ 引脚连接到 LPDDR4 器件的 1.1V 电源,SoC DDR0_CAL 引脚接地。

为 DQ、DQS 和 DM_n 信号提供了 ODT(片上终端)。该器件能够提供三种不同的 ODT 模式:标称、动态和 Park,终端值为:RTT (Park)、RTT (NOM) 和 RTT (WR)。图 4-14 展示了 LPDDR4 和 AM64x 之间的 DDR 接口。

图 4-14 LPDDR4 接口

图 4-14 LPDDR4 接口