ZHCACB2A March 2023 – November 2023 AM2732 , AM2732-Q1

3.1 晶体和振荡器输入选项

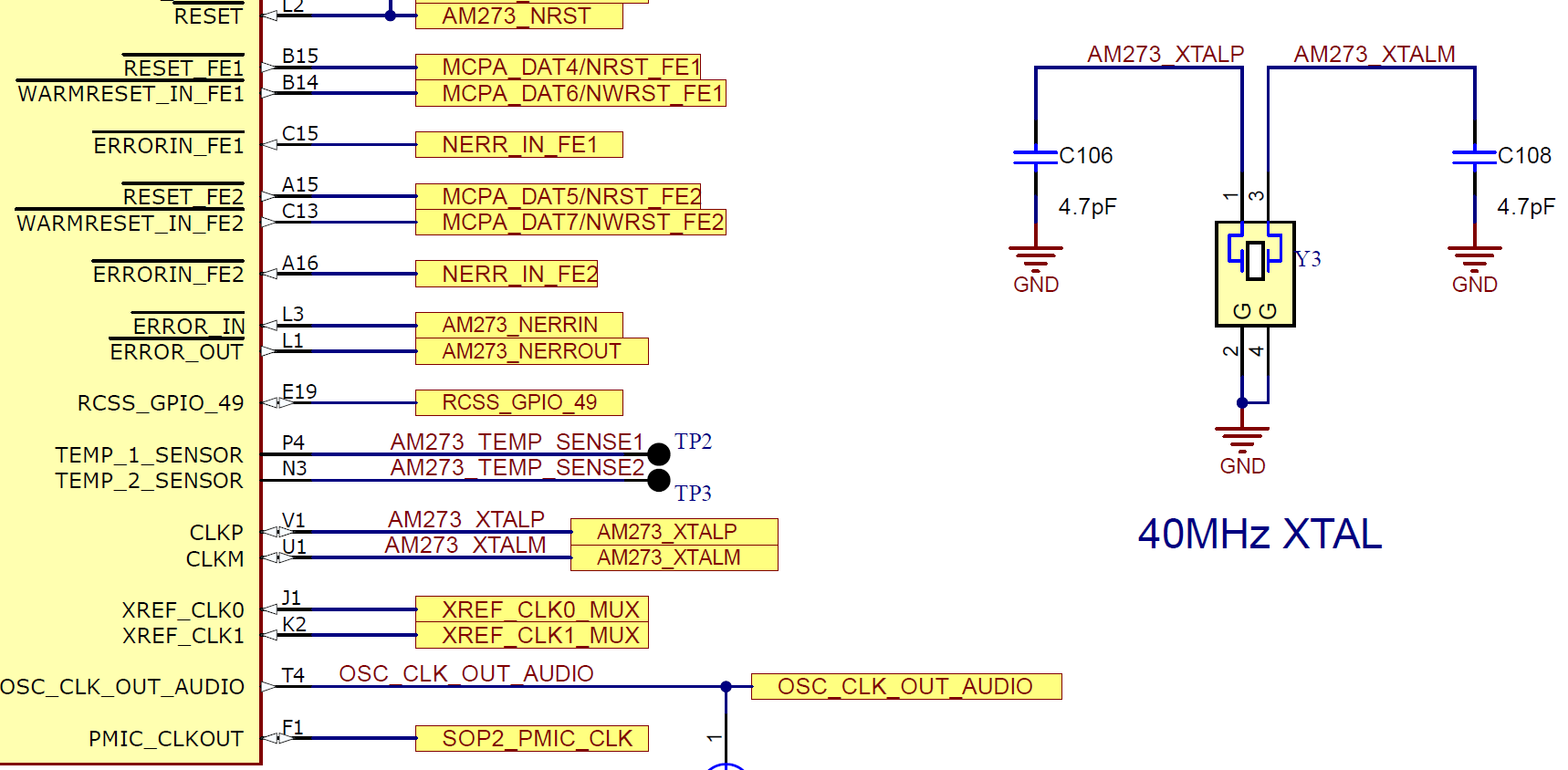

AM273x 主时钟接口 CLKM 和 CLKP(ZCE 引脚 U1 和 V1,NZN 引脚 N1 和 P2)可以由所连接的晶体或单端振荡器输出提供电源。连接的晶体应该是工作频率为 40MHz 的基本模式晶体。如果从单端振荡器输出运行,CLKP 引脚应连接到振荡器,而 CLKM 引脚必须接地。在振荡器输入模式下,CLKP 引脚可以连接到 1.8V 直流耦合方波或交流耦合正弦波振荡器。有关完整的晶体和振荡器输入要求,请参阅 AM273x Sitara™ 微控制器数据表。

图 3-1 摘自 AM273x GPEVM 原理图

图 3-1 摘自 AM273x GPEVM 原理图AM273x 的其他时钟输入包括:

- 两个外部参考时钟输入 XREF_CLK0 和 XREF_CLK1(ZCE 引脚 J1 和 K2,NZN 引脚 G1和 G2),可用作系统同步的专用外设时钟源。

- 两个摄像头子系统 2.0 (CSI2.0) 时钟输入,CSI2_RX0CLKM/CSI2_RX0CLKP(ZCE 引脚 B6 和 A6)用于 CSI2.0 接收器 1,而 CSI2_RX1CLKM/CSI2_RX1CLKP(ZCE 引脚 A11 和 B11)用于 CSI2.0 接收器 2。