ZHCACB2A March 2023 – November 2023 AM2732 , AM2732-Q1

5.2 QSPI 存储器控制器实现

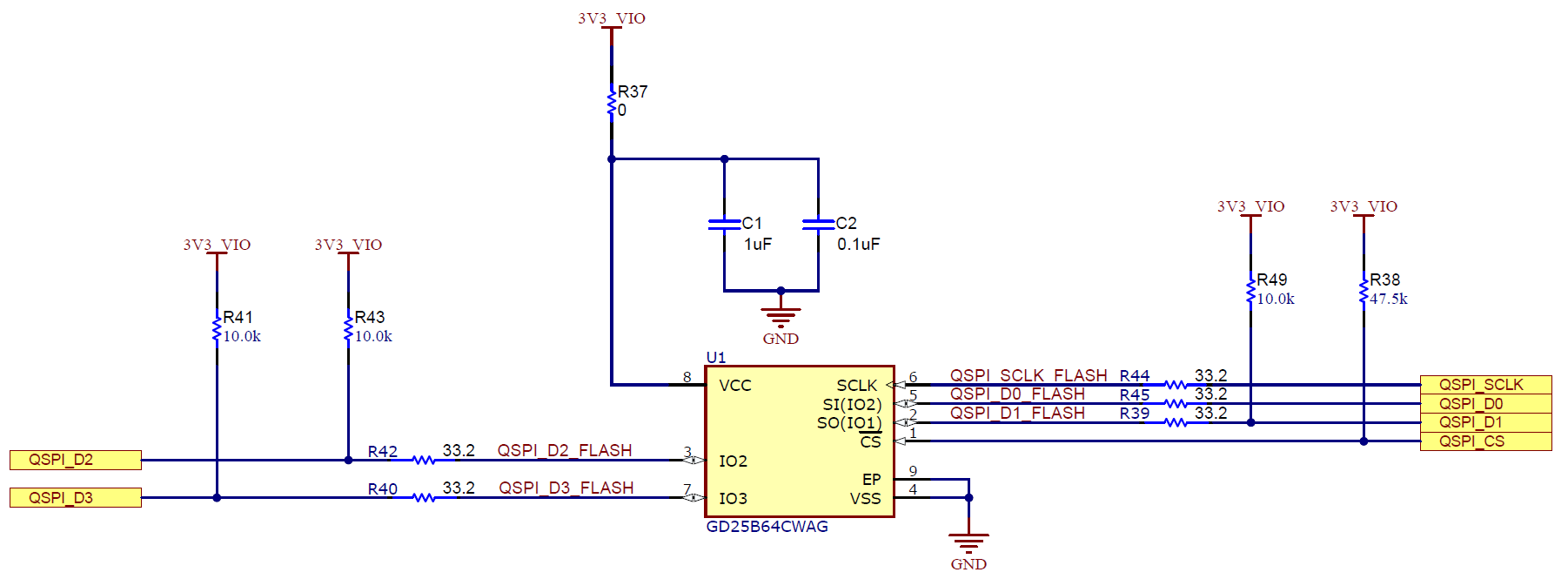

QSPI 存储器是 AM273x MCU 的主要引导存储器位置。此存储器接口的良好信号完整性对于 AM273x MCU 的基本 QSPI 引导操作至关重要。还需要额外的上拉电阻器。

- 包括一个芯片选择上拉电阻器,以确保器件通常处于读取/写入禁用状态,直到 AM273x QSPI 控制器在新的读取/写入事务开始时将芯片选择驱动为低电平。

- 包括一个上拉电阻器,用于在默认情况下禁用写保护模式

- 包括一个上拉电阻器,用于在默认情况下禁用保持模式

图 5-2 摘自 AM273x GPEVM 原理图 – AM273x QSPI 控制器和 GD25B64CWAG NOR 闪存

图 5-2 摘自 AM273x GPEVM 原理图 – AM273x QSPI 控制器和 GD25B64CWAG NOR 闪存图 5-3 和表 5-2 中提供了 QSPI 存储器接口的附加布线指南。这些指南应用作最大布线和偏斜匹配限制。

图 5-3 AM273x QSPI - 布线规则图

图 5-3 AM273x QSPI - 布线规则图表 5-2 AM273x QSPI – 建议的布线规则

| 规格编号 | 规格 | 值 | 单位 |

|---|---|---|---|

| 1 | QSPI_CLK、QSPI_CS0、QSPI_D[3:0] 最大延迟 | 450 | ps |

| 2 | QSPI_CLK 至 QSPI_D[3:0] 最大偏斜 | 50 | ps |

| 3 | 近似最大布线距离 | 3214 | mil |

| 4 | 近似最大布线偏斜 | 357 | mil |

| 5 | 串联端接电阻器(上图中的 R1)应靠近 AM273x 的 QSPI_CLK 发送引脚放置,以控制时钟线路的上升时间和反射。 | 可变,0 到 40 | Ω |

| 6 | 串联端接电阻(上图中的 R2)应靠近所连接存储器的 QSPI 数据引脚放置,以控制数据线路的上升时间和反射。 | 可变,0 到 40 | Ω |

注: 假设 50Ω FR4 微带或带状线传输线路中的传播延迟典型值为 140ps/inch,计算出的近似布线距离。应使用 2D 场求解器或适当的封闭式近似阻抗公式,以找出特定的给定层叠和布线的更精确的传播延迟。

建议将 QSPI 存储器并置于 AM273x BGA 封装附近,这样可以实现使延迟裕度和偏斜裕度达到更大的布线。如图 5-3 所示,还建议在 QSPI 控制器时钟发送引脚附近添加一个串联端接电阻器。同样,也应在 QSPI 器件的数据引脚上添加串联端接。在读取四倍读取操作(将是存储器更常用的工作模式)期间,这有助于在数据线路上创建受控良好的边沿。