ZHCABI5 January 2022 AM67 , AM67A , AM68 , AM68A , AM69 , AM69A , DRA821U , DRA821U-Q1 , DRA829J , DRA829J-Q1 , DRA829V , DRA829V-Q1 , TDA4AEN-Q1 , TDA4AH-Q1 , TDA4AL-Q1 , TDA4AP-Q1 , TDA4APE-Q1 , TDA4VE-Q1 , TDA4VEN-Q1 , TDA4VH-Q1 , TDA4VL-Q1 , TDA4VM , TDA4VM-Q1 , TDA4VP-Q1 , TDA4VPE-Q1

2.1 应用要求

由于 Jacinto 7 采用多核异构架构,因此它不仅集成 Arm A72 内核,还集成 TI 的 C7000 和 C6000 DSP、Arm R5F MCU 内核等。这种多核异构架构不仅性能出众,而且灵活性高且便于设计。

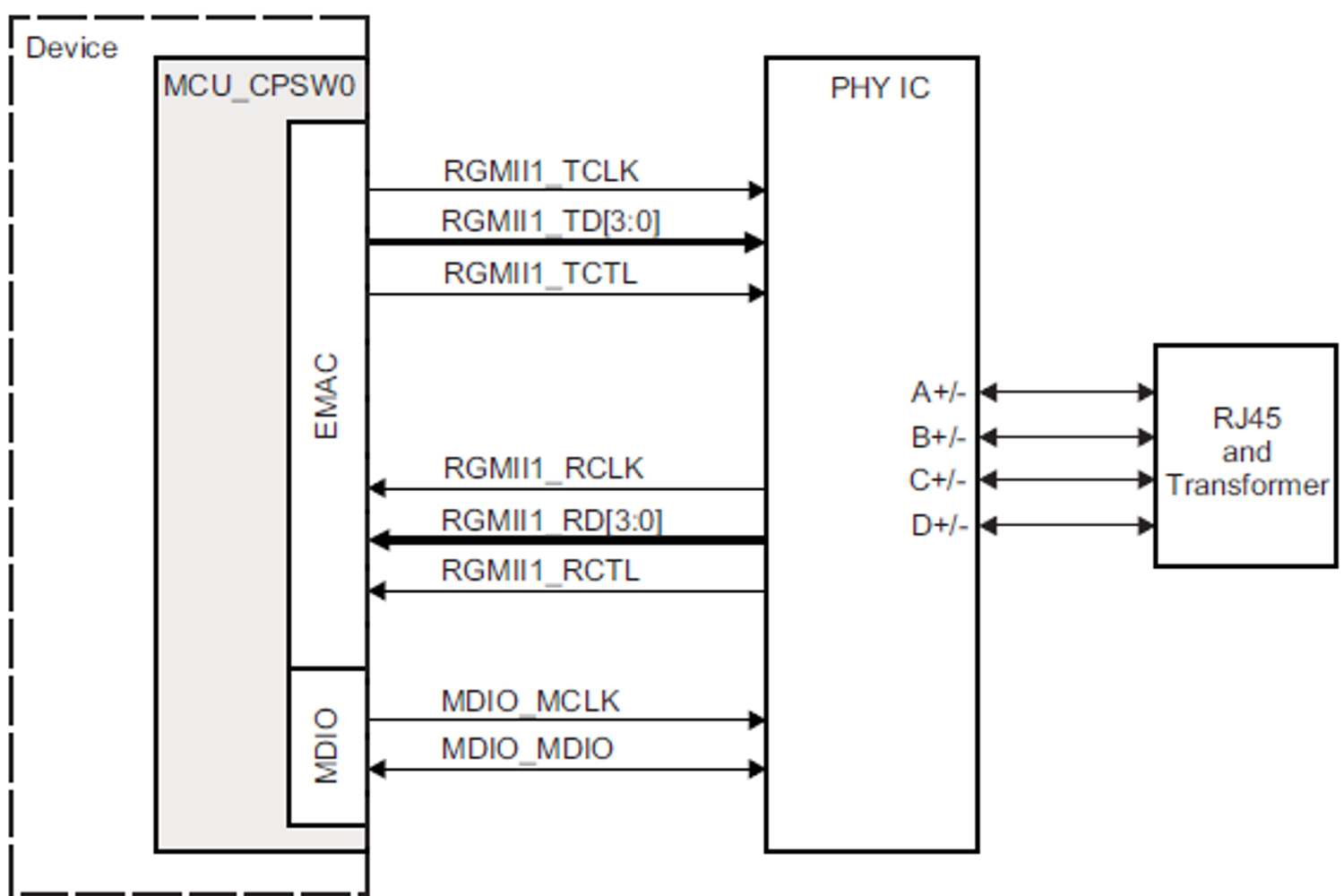

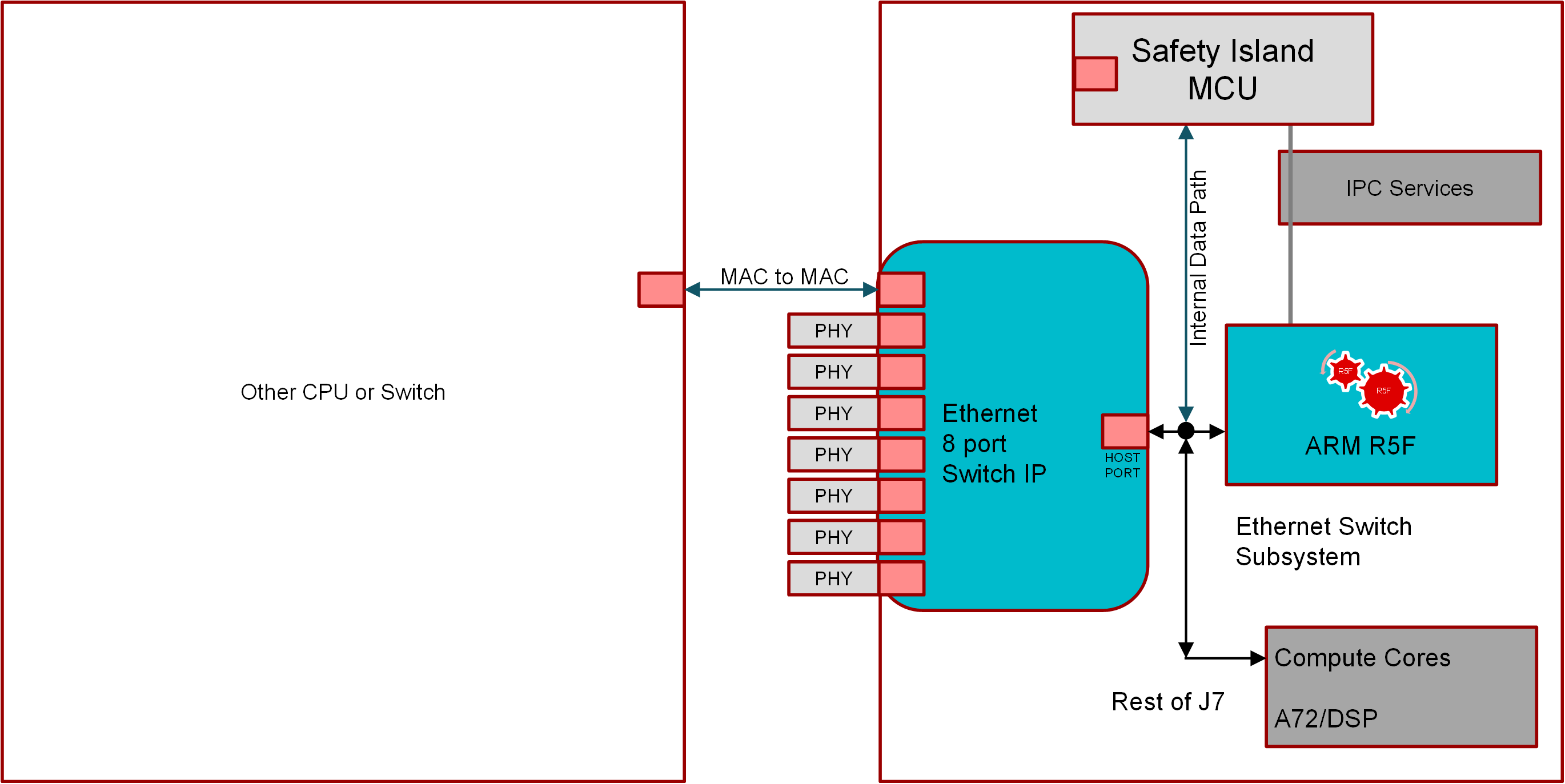

图 2-1 显示 CPSW 的架构。从 MAC 接口类型来看,一般的 RGMII(简化千兆位媒体独立接口)和 SGMII(串行 GMII)可以支持 1000M 以太网。

RGMII 代表简化千兆位媒体独立接口,即引脚数量减少。时钟频率仍然是 125MHz,但 TX/RX 数据位宽从 8 位更改为 4 位。为了在减少数据线路后保持 1Gbps 传输速率不变,在时钟的上升沿和下降沿都发送数据。RGMII 还兼容 100Mbps 和 10Mbps 速率。为此,基准时钟频率分别为 25MHz 和 2.5MHz。图 2-2 显示典型的 RGMII 应用连接。

图 2-2 RGMII 连接

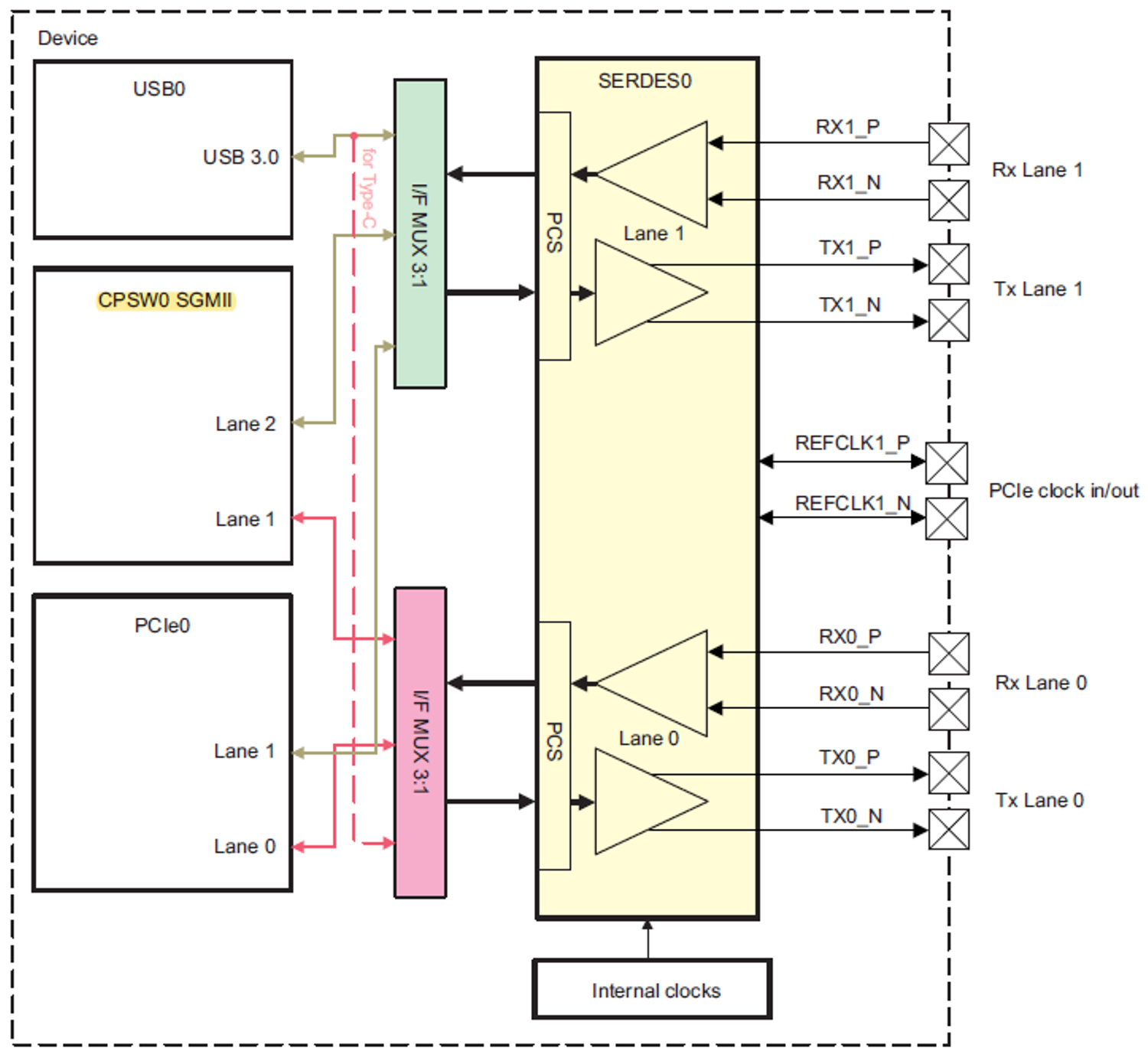

图 2-2 RGMII 连接SGMII 代表串行 GMII,每当需要较高的速度和较少的引脚时会用到。代价是增加了复杂度,需要串行器和解串器模块,该模块简称为 SerDes。它有一对差分信号线,分别用于发送和接收信号。时钟频率为 625MHz,在时钟信号的上升沿和下降沿采样。基准时钟 RX_CLK 可由 PHY 提供,但它是可选的,主要在无时钟时用于 MAC 侧。正常情况下不使用 RX_CLK,传输和接收可以从数据中恢复时钟。大多数 MAC 芯片的 SGMII 接口都可以配置为 SerDes 接口(物理兼容,只需要配置寄存器),直接连接到其他模块,不需要 PHY 层芯片,时钟频率仍然是 625MHz。图 2-3(参考 J721E TRM)显示如何配置有 SerDes 接口的 CPSW SGMII。

图 2-3 Serdes0 概述

图 2-3 Serdes0 概述不同的 SGMII 端口对应不同的 SERDES 通道。表 2-1 显示了这种关系。

| SGMII 端口 | SERDES - 通道 |

|---|---|

| 端口 1 | SERDES 0 - 通道 0 |

| 端口 2 | SERDES 0 - 通道 1 |

| 端口 3 | SERDES 1 - 通道 0 |

| 端口 4 | SERDES 1 - 通道 1 |

| 端口 5 | SERDES 4 - 通道 0 |

| 端口 6 | SERDES 4 - 通道 1 |

| 端口 7 | SERDES 4 - 通道 2 |

| 端口 8 | SERDES 4 - 通道 3 |

因此,MAC2MAC 互连解决方案通常有两种方式,即基于 RGMII 和基于 SGMII。MAC2MAC 可以有许多应用场景,这里说明其中 3 种:

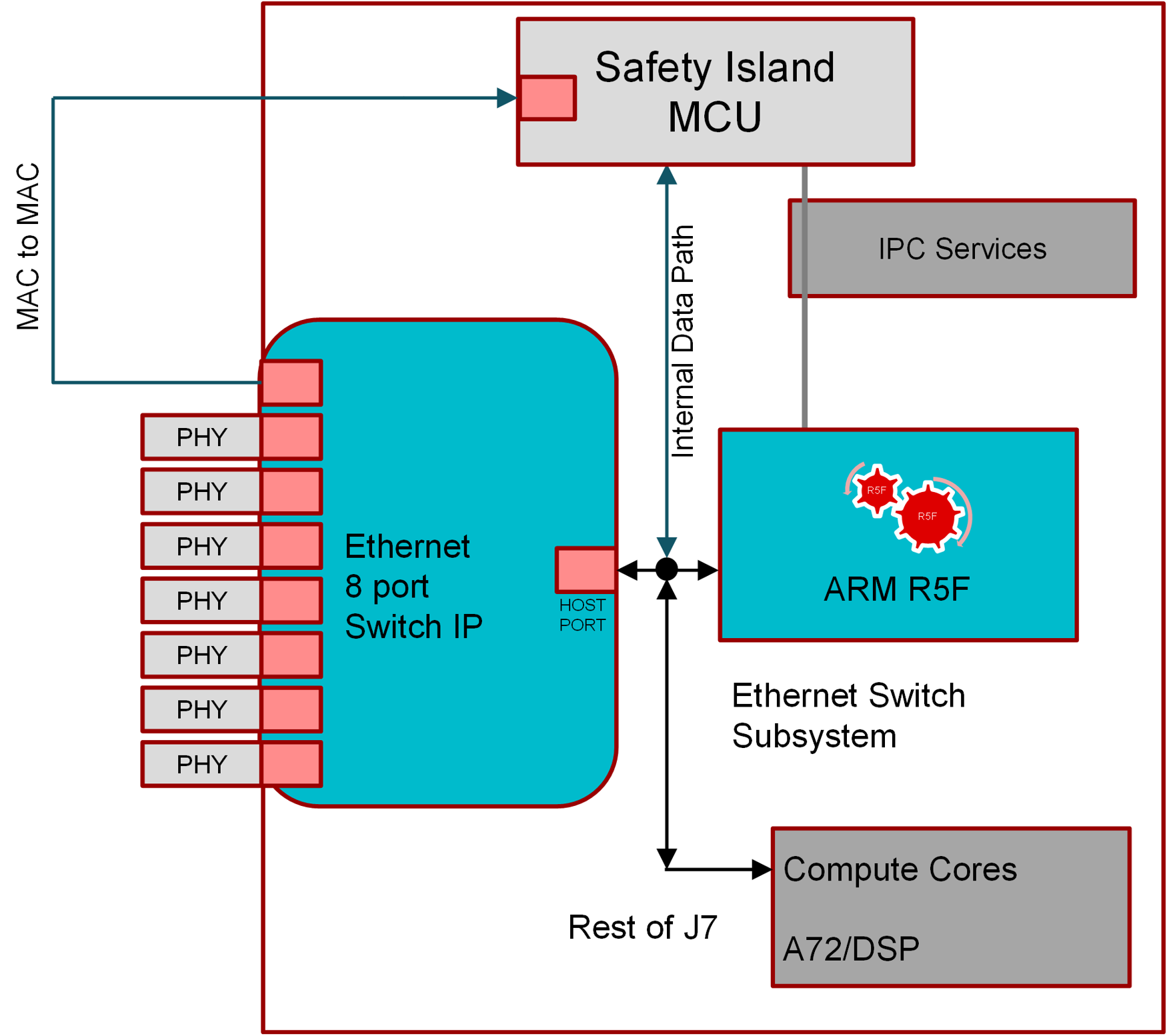

- Jacinto7 分为两部分,MCU 域和主域。CPSW2G 通常分配给 MCU 域,CPSW9G 通常由主域内核 A72 和 R5F 使用。鉴于功能安全要求,MCU 域通常使用 AUTOSAR OS。除了内部数据路径,从外部看,通过 MAC2MAC 连接两个交换机也非常方便。图 2-4 显示系统架构。

图 2-4 CPSW9G 和 CPSW2G MAC2MAC

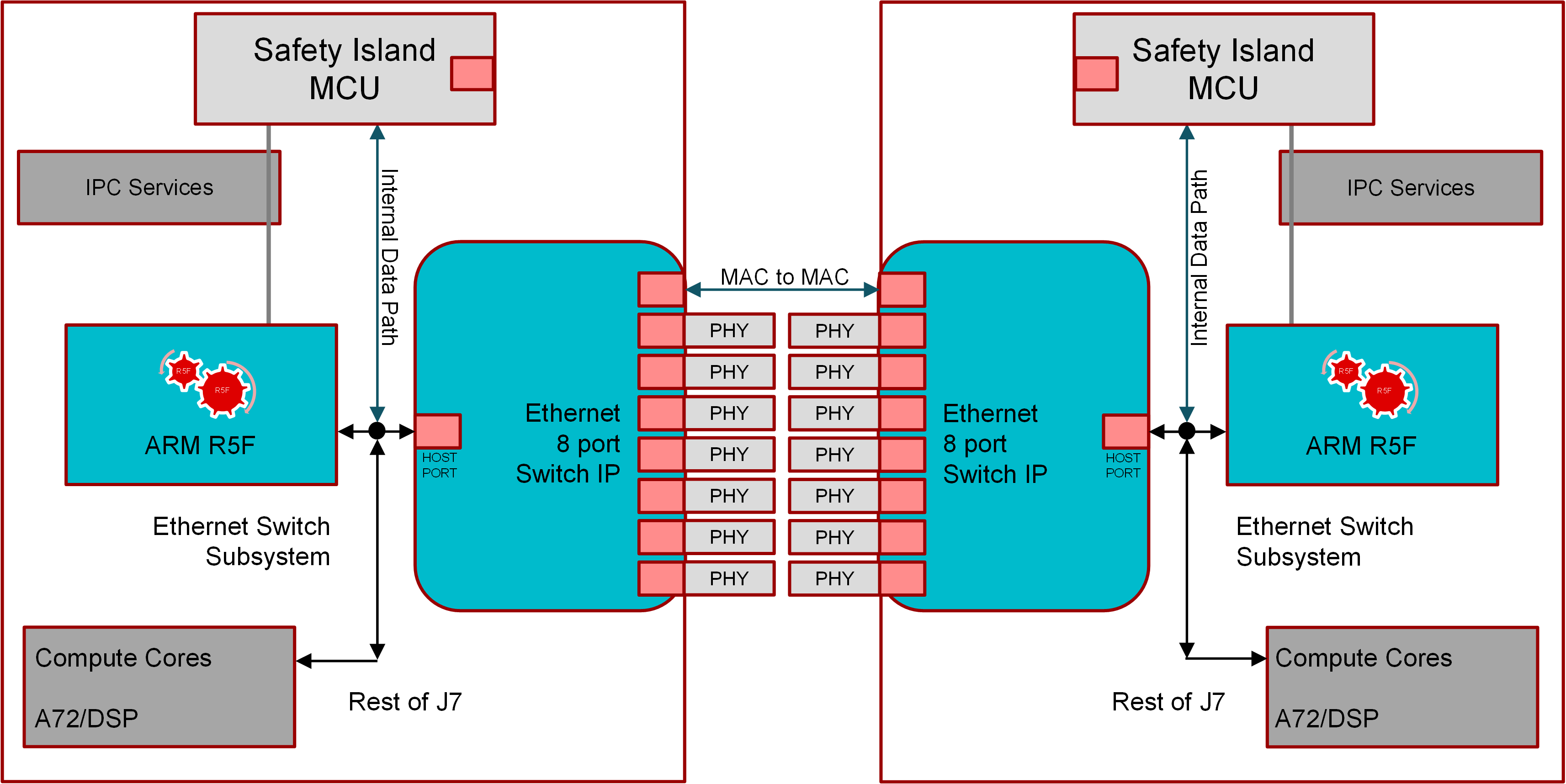

图 2-4 CPSW9G 和 CPSW2G MAC2MAC - 当单个 Jactinto7 处理器的性能不能满足系统要求时,将多个 Jactinto7 SOC 集成在一块电路板上也是非常方便的。在这种情况下,有助于通过 MAC2MAC 连接 CPSW 交换机。图 2-5 显示系统方框图。

图 2-5 SOC 与 SOC 之间的 MAC2MAC

图 2-5 SOC 与 SOC 之间的 MAC2MAC - MAC2MAC 可用于连接外部交换机或其他 SoC 上的 MAC。它有两个目的,第一是增加端口数,第二是可用来互连 SoC。图 2-6 显示系统方框图。

图 2-6 外部 Soc 连接到 TDA4VM

图 2-6 外部 Soc 连接到 TDA4VM