ZHCUCH8B November 2024 – November 2025 AM2612

- 1

- 说明

- 开始使用

- 特性

- 5

- 1评估模块概述

-

2硬件

- 2.1 设置

- 2.2 电源要求

- 2.3 接头信息

- 2.4 按钮

- 2.5 复位

- 2.6 时钟

- 2.7 引导模式选择

- 2.8 GPIO 映射

- 2.9 IO 扩展器

- 2.10 接口

- 2.11 BoosterPack 接头

- 2.12 引脚多路复用映射

- 2.13 测试点

- 2.14 最佳实践

- 3软件

- 4硬件设计文件

- 5合规性

- 6其他信息

- 7参考资料

- 8修订历史记录

2.10.12 ADC 和 DAC

AM261x LaunchPad 会将 20 路 ADC 输入映射到 BoosterPack 接头。该 LaunchPad 中使用的所有 ADC 输入都受到 ESD 保护。

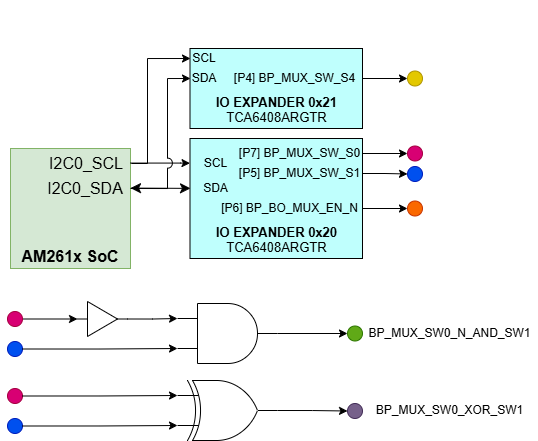

有多个多路复用器根据所选的 BoosterPack 模式决定 ADC 输入信号的路径。下表显示了 BoosterPack 模式多路复用器中使用的多路复用器选择信号逻辑。

图 2-29 BoosterPack 模式多路复用器选择逻辑

图 2-29 BoosterPack 模式多路复用器选择逻辑表 2-44 多路复用器选择逻辑输出

| BP_MUX_SW_S0 | BP_MUX_SW_S1 | BP_MUX_SW0_N_AND_SW1 | BP_MUX_SW0_XOR_SW1 |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 0 |

图 2-30 ADC/DAC 接口

图 2-30 ADC/DAC 接口ADC 和 DAC 需要电压基准。AM261x LaunchPad 具有两个开关,让用户可以在 ADC 和 DAC 电压基准之间进行选择。

图 2-31 ADC 和 DAC VREF 开关

图 2-31 ADC 和 DAC VREF 开关 图 2-32 LP-AM261 ADC/DAC VREF 开关

图 2-32 LP-AM261 ADC/DAC VREF 开关DAC VREF 开关 (S1) 是一个单极双掷开关,用于控制 AM261x SoC 的 ADC VREF 输入。

注: DAC VREF 开关必须位于引脚 1-2 位置,SDK 示例才能正常工作。

表 2-45 DAC VREF 开关

| DAC VREF 开关位置 | 基准选择 |

|---|---|

| 引脚 1-2(左侧) | AM261x 片上 LDO |

| 引脚 2-3(右侧) | 外部 DAC VREF 接头 |

ADC VREF 开关 (S2) 包含两个单极双掷开关,用于控制 AM261x SoC 的 ADC VREF 输入。

注: ADC VREF 开关必须位于 1-2 和 4-5 位置,SDK 示例才能正常工作。

表 2-46 ADC VREF 开关

| ADC VREF 开关位置 | 基准选择 |

|---|---|

| 引脚 1-2(下方) | 板载 PMIC 1.8V 输出 |

| 引脚 2-3(上方) | 外部 ADC VREF 接头 |

| 引脚 4-5(下方) | 板载 PMIC 1.8V 输出 |

| 引脚 5-6(上方) | 外部 ADC VREF 接头 |