ZHCUCH8B November 2024 – November 2025 AM2612

- 1

- 说明

- 开始使用

- 特性

- 5

- 1评估模块概述

-

2硬件

- 2.1 设置

- 2.2 电源要求

- 2.3 接头信息

- 2.4 按钮

- 2.5 复位

- 2.6 时钟

- 2.7 引导模式选择

- 2.8 GPIO 映射

- 2.9 IO 扩展器

- 2.10 接口

- 2.11 BoosterPack 接头

- 2.12 引脚多路复用映射

- 2.13 测试点

- 2.14 最佳实践

- 3软件

- 4硬件设计文件

- 5合规性

- 6其他信息

- 7参考资料

- 8修订历史记录

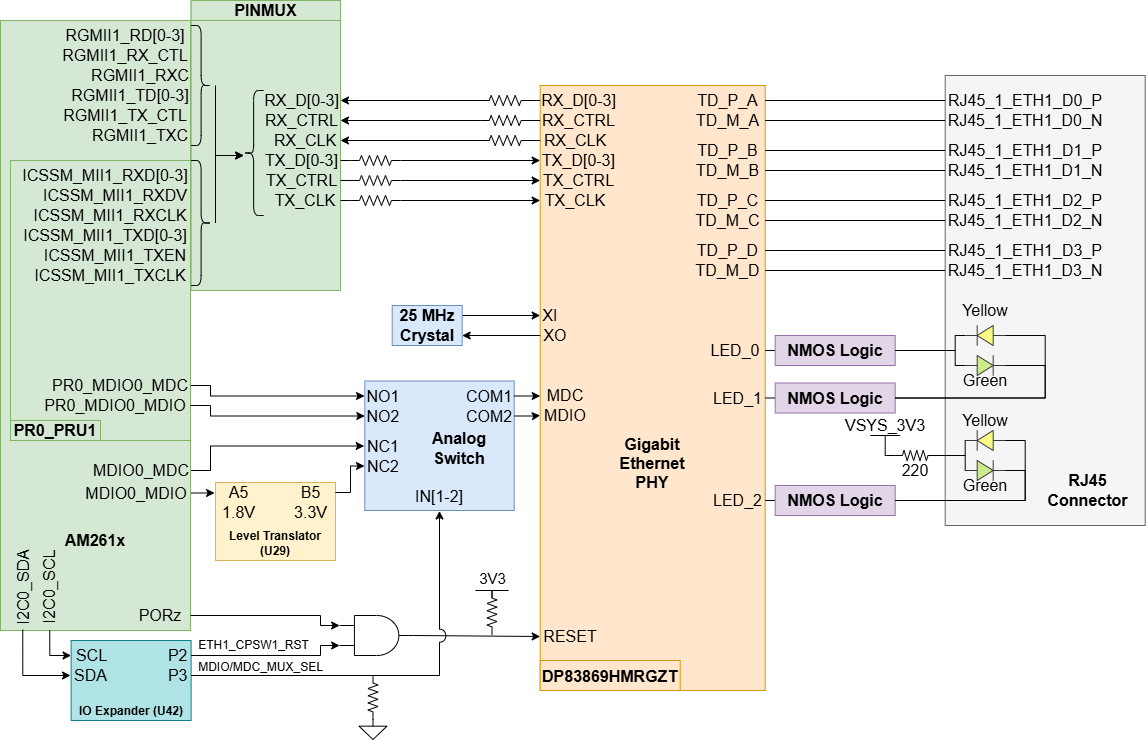

2.10.2.2 以太网 PHY 1 — RGMII1/PR0_PRU1

AM261x LaunchPad 采用一个 48 引脚以太网 PHY (DP83869HMRGZT),该 PHY 连接到 RGMII1 或片上可编程实时单元和工业通信子系统 (PRU-ICSS) 的 PR0_PRU1 实例。RGMII1 和 PR0_PRU1 信号在 AM261x MCU 上进行内部引脚多路复用,并且可以根据应用程序通过软件控制。

该 PHY 配置为广播 1Gb 操作。该 PHY 的以太网数据信号端接至 RJ45 连接器。电路板使用 RJ45 连接器来提供以太网 10/100/1000Mbps 连接,并集成电磁元件和 LED 来提供链路和活动指示。

图 2-18 以太网 PHY 1

图 2-18 以太网 PHY 1该以太网 PHY 需要三个单独的电源。VDDIO 是系统生成的 3.3V 电源。以太网 PHY 的 1.1V 和 2.5V 电源各有一个专用 LDO。

靠近 SoC 的发送时钟和数据信号上存在串联终端电阻器。靠近以太网 PHY 的接收时钟和数据信号上存在串联终端电阻器。

从 AM261x MCU 到 PHY 的 CPSW MDIO 数据信号通过双向电平转换器传递,以便将 IO 电平从 1.8V 转换为 3.3V,以实现与 DP83869 PHY 的兼容性。CPSW MDIO 时钟信号源自 AM261x MCU 的 3.3V IO 引脚,因此不需要电平位移。由于 CPSW 以太网和 PRU 以太网具备单独的 MDIO 信号,因此模拟开关 (TS5A23159DGSR/U48) 负责在 CPSW MDIO/MDC 和 PRU MDIO/MDC 信号之间进行选择并将所选信号路由至以太网 PHY。该模拟开关由受 I2C 控制的 IO 扩展器 (U42) 的 GPIO 信号进行控制。

| MDIO/MDC_MUX_SEL | 条件 | 开关功能 |

|---|---|---|

| LOW(默认值) | CPSW MDIO | NC 至 COM,COM 至 NC |

| 高电平 | PRU MDIO | NO 至 COM,COM 至 NO |

以太网 PHY 的复位输入由 PORz AM261x MCU 输出信号 ANDed 与受 I2C 控制的 IO 扩展器 (U42) ETH1_CPSW1_RST 的输出进行控制。

以太网 PHY 使用很多功能引脚用作 Strap 配置选项,以便将器件置于特定的运行模式。

| 功能引脚 | 默认模式 | LP 中的模式 | 功能 |

|---|---|---|---|

| RX_D0 | 0 | 0 | PHY 地址:1100 |

| RX_D1 | 0 | 3 | |

| JTAG_TDO/GPIO_1 | 0 | 0 | RGMII 至铜线 |

| RX_D3 | 0 | 0 | |

| RX_D2 | 0 | 0 | |

| LED_0 | 0 | 0 | 自动协商,广播 1000/100/10,自动 MDI-X |

| RX_ER | 0 | 0 | |

| LED_2 | 0 | 0 | |

| RX_DV | 0 | 0 | 端口镜像已禁用 |