ZHCUCH8B November 2024 – November 2025 AM2612

- 1

- 说明

- 开始使用

- 特性

- 5

- 1评估模块概述

-

2硬件

- 2.1 设置

- 2.2 电源要求

- 2.3 接头信息

- 2.4 按钮

- 2.5 复位

- 2.6 时钟

- 2.7 引导模式选择

- 2.8 GPIO 映射

- 2.9 IO 扩展器

- 2.10 接口

- 2.11 BoosterPack 接头

- 2.12 引脚多路复用映射

- 2.13 测试点

- 2.14 最佳实践

- 3软件

- 4硬件设计文件

- 5合规性

- 6其他信息

- 7参考资料

- 8修订历史记录

2.5 复位

图 2-7 展示了 AM261x LaunchPad 的复位架构

图 2-7 复位架构

图 2-7 复位架构AM261x LaunchPad 具有以下复位:

- PORz(上电复位)

- WARMRESETn(热复位)

图 2-8 PORZ

复位信号树

图 2-8 PORZ

复位信号树PORz

PORz 信号由 2 路输入与门驱动,后者会在以下情况下生成主域上电复位:

- PMIC 的 (TPS650360) NRSTOUT 被驱动为低电平

- 按下用户按钮 (SW1) 时。

- P 沟道

MOSFET 栅极的信号为逻辑低电平,这会导致 PMOS 的 VGS

小于零。PORz 信号连接至直接接地的 PMOS 漏极。可为 PMOS

栅极生成逻辑低电平输入的信号包括:

- 来自测试自动化接头的 TA_PORZ 输出

- 来自任一 BoosterPack 站点的 BP_PORZ 输出。

PORz 信号连接到:

- AM261x SoC PORz 输入

- 两个以太网附加电路板连接器复位逻辑

- 引导模式状态驱动器

(U61) 的输出使能输入

- RC 滤波器在 GND 与 3.0V 电源之间产生 1ms 的延迟,以便 SOP 状态驱动器的输出使能输入保持低电平的时间超过 PORz 取消置位后所需的 SOP 保持时间。

WARMRESETn

WARMRESETn 信号会在以下情况下生成主域热复位:

- 按下用户按钮 (SW2) 时。

WARMRESETn 信号连接到:

- AM261x SoC WARMRESETN 输出

- 按下按钮+ PMOS 逻辑生成的 RESETN_PB 信号

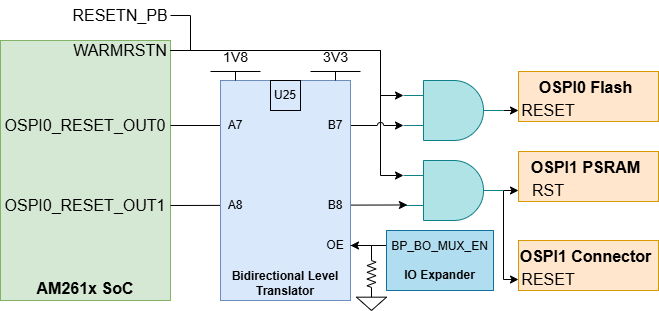

- OSPI0 和 OSPI1 器件复位逻辑

图 2-9 WARMRESETn

复位信号树

图 2-9 WARMRESETn

复位信号树

注: OSPI0_RESET_OUT0 由 GPIO61 通过引脚多路复用产生,而 GPIO61 存在一个与 AM261x

引导 ROM 关联的已知问题。在引导时,ROM 代码将 GPIO61 设置为 OSPI0_RESET_OUT0

并将引脚驱动为低电平,以复位外部闪存器件。但是,由于 OSPI

控制器配置中的错误,闪存器件复位后,该引脚不会驱动为高电平,从而使闪存器件保持在复位状态并阻止正常引导。默认情况下,通过连接到输出使能引脚的拉电阻器来禁用双向电平转换器

(U25)。这样可以防止(GPIO61 上的)OSPI0_RESET_OUT0 在器件从 OSPI0

闪存引导之前将输入拉至与门低电平。OSPI0_RESET_OUT0 网络在与门处被上拉至高电平。器件引导后,可在软件中将

OSPI0_RESET_OUT0 配置为 OSPI 复位,并可从 I2C 控制的 IO 扩展器 (U23)

启用电平转换器 (U25)。有关此引导 ROM 问题的更多信息,请参阅 AM261x

勘误文档。

INTn

AM261x LaunchPad 还具有 SoC 的外部中断 INT1,以下情况下会发生该中断:

- 按下用户按钮 (SW3) 时